## 修士論文

## 宇宙硬X線撮像用 低ノイズ両面シリコンストリップ検出器の開発

M1379004 宇野 進吾

広島大学大学院理学研究科物理科学専攻 素粒子実験・高エネルギー宇宙学研究室

平成 15 年 3 月 16 日

現在の宇宙観測では数 10keV ~ 数 MeV の領域は他のエネルギー帯に比べて感度の向上が遅れている。この領域はコンプトン散乱が支配的であり、光子のエネルギーや到来方向を高精度で測定することが難しく、性能の良い検出器が開発されてこなかったからである。しかし、このエネルギー領域には高エネルギー天体からの非熱的放射、銀河の星の生成過程を知る手がかりになる超新星爆発起源の核ガンマ線など、非常に重要な物理が含まれている。そこで、現在我々のグループが感度向上のために開発を行っているのが多重コンプトンガンマ線カメラである。検出器に入射してきた光子が複数回のコンプトン散乱を行った場合、反応位置と落としたエネルギーを高精度で測定することができれば、コンプトン散乱の運動学を解くことにより、光子の到来方向を制限することができる。多重コンプトンガンマ線カメラは位置検出型半導体検出器を多層構造にすることで位置決定精度と反応率を上げ、この領域で今までにない感度を達成することが期待される。

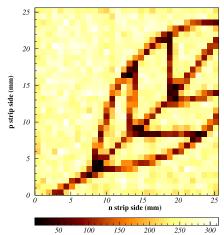

本研究では、こうしたガンマ線カメラの構成要素として高いエネルギー分解能を持つ両面シリコンストリップ検出器 (SSD) の開発とその読み出し、さらには非常にコンパクトで汎用性の高い新しい読み出しシステムを立ち上げ、SSD の読み出しに成功した。CCD ではなく SSD を使うことにより、高エネルギー側にも感度を持ち、バックグラウンドの多い硬 X 線ガンマ線領域で必要な高速読み出しが可能となる。SSD の構造の最適化としては、電極の太さや電圧降伏を起こさないストリップ間距離について考察した。また、光子の到来方向の決定精度は検出器のエネルギー分解能に大きく依存し、1 keV くらいのエネルギー分解能で理論的限界になるが、片面 SSD では1 keV に近いエネルギー分解能を達成した。複数チャンネル同時計測でこのような良い報告は世界的に見ても他に例がない。多重コンプトンガンマ線カメラで必要な両面 SSD の撮像も行い、両面 SSD で2次元位置情報、エネルギー情報が正確に得られることを確認した。

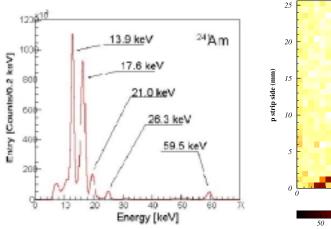

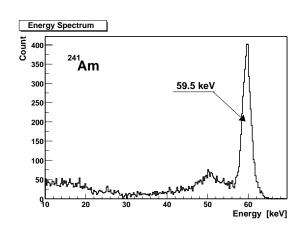

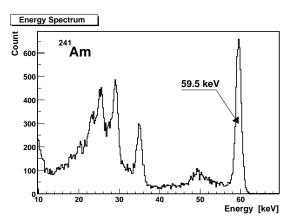

片面 SSD の複数チャンネル同時計測で得られた  $^{241}{

m Am}$  のスペクトル (左) と両面 SSD で得られた「リーフ」のイメージ

# 目 次

|                                               | 序論                                                                                                                                                                                                                                                                    | 8                                                           |

|-----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|

| 1.1                                           | X 線ガンマ線天体物理学                                                                                                                                                                                                                                                          |                                                             |

| 1.2                                           | 多重コンプトンガンマ線カメラ                                                                                                                                                                                                                                                        | 9                                                           |

| 第2章                                           | 半導体検出器の基礎特性とシリコンストリップ検出器                                                                                                                                                                                                                                              | 12                                                          |

| 2.1                                           | 半導体を用いた放射線検出器の検出原理・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                                                                                                                                                                                                                | 12                                                          |

| 2.2                                           | pn 接合ダイオード                                                                                                                                                                                                                                                            | 12                                                          |

| 2.3                                           | シリコンストリップ検出器の基礎                                                                                                                                                                                                                                                       | 13                                                          |

|                                               | 2.3.1 シリコンストリップ検出器の構造                                                                                                                                                                                                                                                 | 13                                                          |

|                                               | 2.3.2 Leakage Current                                                                                                                                                                                                                                                 | 14                                                          |

|                                               | 2.3.3 Body Capacitance L Inter-strip Capacitance                                                                                                                                                                                                                      | 15                                                          |

|                                               | 2.3.4 両面シリコンストリップの構造                                                                                                                                                                                                                                                  | 16                                                          |

| 2.4                                           | シリコンストリップ検出器の読み出し                                                                                                                                                                                                                                                     | 17                                                          |

|                                               | 2.4.1 半導体検出器の信号処理                                                                                                                                                                                                                                                     | 17                                                          |

|                                               | 2.4.2 シリコンストリップ検出器のエネルギー分解能                                                                                                                                                                                                                                           | 18                                                          |

|                                               |                                                                                                                                                                                                                                                                       |                                                             |

| 第3章                                           | シリコンストリップ検出器の性能評価                                                                                                                                                                                                                                                     | 21                                                          |

| 第 <b>3章</b><br>3.1                            |                                                                                                                                                                                                                                                                       |                                                             |

|                                               | エネルギー分解能を上げるための工夫                                                                                                                                                                                                                                                     | 21                                                          |

| 3.1<br>3.2                                    | エネルギー分解能を上げるための工夫                                                                                                                                                                                                                                                     | 21<br>23                                                    |

| 3.1<br>3.2<br>3.3                             | エネルギー分解能を上げるための工夫                                                                                                                                                                                                                                                     | 21<br>23<br>27                                              |

| 3.1<br>3.2<br>3.3<br>3.4                      | エネルギー分解能を上げるための工夫         I-V curve, C-V curve         X 線によるエネルギー分解能の測定         1 ストリップあたりの X 線検出領域                                                                                                                                                                  | 21<br>23<br>27<br>30                                        |

| 3.1<br>3.2<br>3.3<br>3.4<br>3.5               | エネルギー分解能を上げるための工夫         I-V curve, C-V curve          X 線によるエネルギー分解能の測定          1 ストリップあたりの X 線検出領域          TypeB のリーク電流、Body Capacitance の考察                                                                                                                     | 21<br>23<br>27<br>30<br>33                                  |

| 3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6        | エネルギー分解能を上げるための工夫         I-V curve, C-V curve         X 線によるエネルギー分解能の測定         1 ストリップあたりの X 線検出領域         TypeB のリーク電流、Body Capacitance の考察         片面シリコンストリップ検出器のまとめ                                                                                             | 21<br>23<br>27<br>30<br>33<br>34                            |

| 3.1<br>3.2<br>3.3<br>3.4<br>3.5               | エネルギー分解能を上げるための工夫I-V curve, C-V curveX 線によるエネルギー分解能の測定1 ストリップあたりの X 線検出領域TypeB のリーク電流、Body Capacitance の考察片面シリコンストリップ検出器のまとめ両面シリコンストリップ検出器の性能評価                                                                                                                       | 21<br>23<br>27<br>30<br>33<br>34<br>35                      |

| 3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6        | エネルギー分解能を上げるための工夫I-V curve, C-V curveX線によるエネルギー分解能の測定1 ストリップあたりの X 線検出領域TypeB のリーク電流、Body Capacitance の考察片面シリコンストリップ検出器のまとめ両面シリコンストリップ検出器の性能評価3.7.1 試作した DSSD の基本設計                                                                                                   | 21<br>23<br>27<br>30<br>33<br>34<br>35<br>35                |

| 3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6        | エネルギー分解能を上げるための工夫I-V curve, C-V curveX線によるエネルギー分解能の測定1 ストリップあたりの X 線検出領域TypeB のリーク電流、Body Capacitance の考察片面シリコンストリップ検出器のまとめ両面シリコンストリップ検出器の性能評価3.7.1 試作した DSSD の基本設計3.7.2 I-V curve, C-V curve                                                                         | 21<br>23<br>27<br>30<br>33<br>34<br>35<br>36                |

| 3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6        | エネルギー分解能を上げるための工夫 I-V curve,C-V curve X 線によるエネルギー分解能の測定 1 ストリップあたりの X 線検出領域 TypeB のリーク電流、Body Capacitance の考察 片面シリコンストリップ検出器のまとめ 両面シリコンストリップ検出器の性能評価 3.7.1 試作した DSSD の基本設計 3.7.2 I-V curve, C-V curve 3.7.3 Test structure を用いた p+ ストリップ間距離の最適化                       | 211<br>23<br>27<br>30<br>33<br>34<br>35<br>36<br>38         |

| 3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7 | エネルギー分解能を上げるための工夫I-V curve, C-V curveX線によるエネルギー分解能の測定1 ストリップあたりの X 線検出領域TypeB のリーク電流、Body Capacitance の考察片面シリコンストリップ検出器のまとめ両面シリコンストリップ検出器の性能評価3.7.1 試作した DSSD の基本設計3.7.2 I-V curve, C-V curve3.7.3 Test structure を用いた p+ ストリップ間距離の最適化3.7.4 両面シリコンストリップ検出器のエネルギー分解能測定 | 21<br>23<br>27<br>30<br>33<br>34<br>35<br>36<br>38<br>39    |

| 3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6        | エネルギー分解能を上げるための工夫 I-V curve,C-V curve X 線によるエネルギー分解能の測定 1 ストリップあたりの X 線検出領域 TypeB のリーク電流、Body Capacitance の考察 片面シリコンストリップ検出器のまとめ 両面シリコンストリップ検出器の性能評価 3.7.1 試作した DSSD の基本設計 3.7.2 I-V curve, C-V curve 3.7.3 Test structure を用いた p+ ストリップ間距離の最適化                       | 211<br>233<br>277<br>300<br>333<br>344<br>355<br>366<br>388 |

| 3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7 | エネルギー分解能を上げるための工夫I-V curve, C-V curveX線によるエネルギー分解能の測定1 ストリップあたりの X 線検出領域TypeB のリーク電流、Body Capacitance の考察片面シリコンストリップ検出器のまとめ両面シリコンストリップ検出器の性能評価3.7.1 試作した DSSD の基本設計3.7.2 I-V curve, C-V curve3.7.3 Test structure を用いた p+ ストリップ間距離の最適化3.7.4 両面シリコンストリップ検出器のエネルギー分解能測定 | 21<br>23<br>27<br>30<br>33<br>34<br>35<br>36<br>38<br>39    |

|     | 4.1.1 VA32TA とその特徴                           | 44         |

|-----|----------------------------------------------|------------|

|     | 4.1.2 VA32TA の動作に必要な制御信号                     | 47         |

|     | 4.1.3 VA32TA の動作原理                           | 49         |

| 4.2 | フロントエンドカード                                   | 50         |

| 4.3 | VA-DAQ                                       | 51         |

| 4.4 | 新しい読み出しシステム                                  | 53         |

|     | 4.4.1 システムの概要                                | 53         |

| 第5章 | VA32TA を用いたシリコンストリップ検出器の多チャンネル同時計測           | 58         |

| 5.1 | 実験セットアップ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・  | 58         |

| 5.2 | データ解析の方法・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・ | 58         |

| 5.3 | VA32TA を用いた SSD 読み出しシステムの性能評価                | 60         |

| 第6章 | シリコンストリップ検出器による硬 X 線の撮像                      | <b>6</b> 4 |

| 6.1 | 両面シリコンストリップ検出器の読み出しに向けて                      | 64         |

| 6.2 | 両面シリコンストリップ検出器の両面同時読み出し                      | 64         |

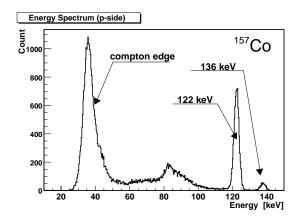

| 6.3 | フラットイメージ                                     | 67         |

| 6.4 | 位置情報の検定・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・  | 68         |

| 6.5 | DSSD <b>を用いた硬</b> X 線 <b>の</b> 撮像            | 71         |

| 6.6 | スプリットイベントに対する考察                              | 71         |

| 6.7 | ROC を用いたシリコンストリップ検出器の読み出し                    | 74         |

| 第7章 | まとめ                                          | 77         |

# 図目次

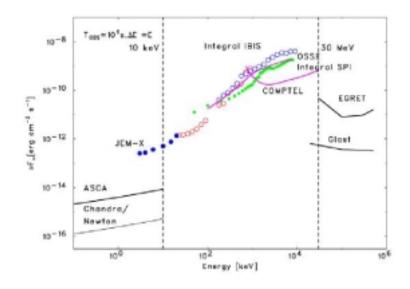

| 1.1  | さまざまな観測衛星の感度の比較。横軸はX線、ガンマ線のエネルギー、                                |    |

|------|------------------------------------------------------------------|----|

|      | 縦軸は感度を表す。                                                        | Ĝ  |

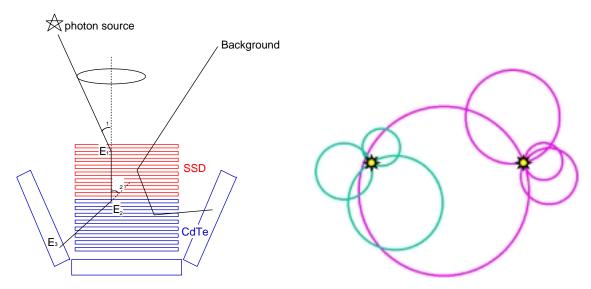

| 1.2  | (a) 多重コンプトンガンマ線カメラの基本構造。散乱体として SSD、CdTe                          |    |

|      | ピクセル検出器を用いる。天体からのX線、ガンマ線は散乱体で複数回の                                |    |

|      | コンプトン散乱を繰り返し、吸収体で光電吸収を起こす。(b) 数イベントの                             |    |

|      | 重ね合わせ。円弧が重なり合っているところが天体の位置になる。円弧の                                |    |

|      | 太さは検出器のエネルギー分解能に依存する。                                            | 10 |

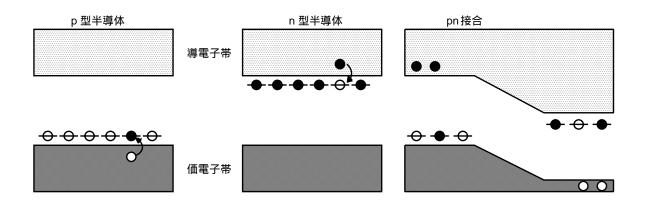

| 2.1  | n 型、p 型半導体と pn 接合のバンドギャップ内にできる新しいエネルギー                           |    |

|      | レベル                                                              | 13 |

| 2.2  | シリコンストリップ検出器の基本構造。 $\mathrm{n}$ バルク内で $\mathrm{X}$ 線が光電吸収を起      |    |

|      | こした場合、エネルギーに比例した電子ホール対ができ、内部電場に従っ                                |    |

|      | て電極に収集される。                                                       | 14 |

| 2.3  | Body Capacitance $\succeq$ Interstrip Capacitance                | 15 |

| 2.4  | 両面シリコンストリップ検出器の基本構造                                              | 16 |

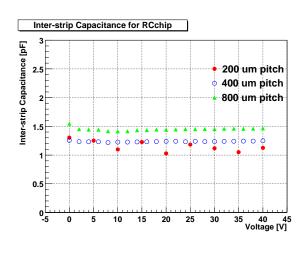

| 2.5  | n <sup>+</sup> ストリップの Inter-strip Capacitance                    | 17 |

| 2.6  | 半導体検出器の一般的な信号処理回路図                                               | 17 |

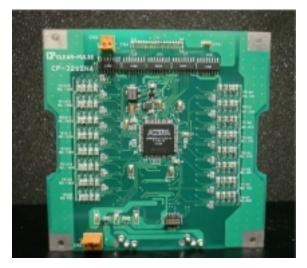

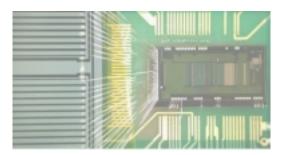

| 3.1  | 多重コンプトンガンマ線カメラの基礎研究用に製作した SSD と RCchip                           | 21 |

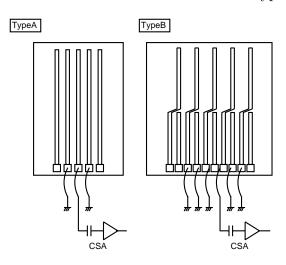

| 3.2  | TypeA、TypeB の上面図と断面図                                             | 22 |

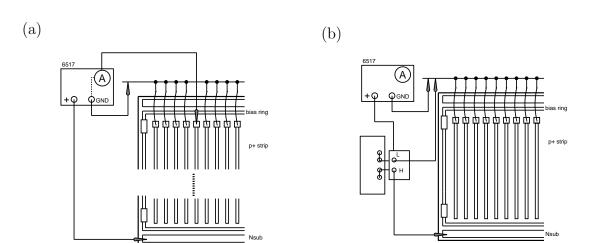

| 3.3  | (a) リーク電流の測定セットアップ (b)Body Capacitance の測定セット                    |    |

|      | アップ (c)Inter-strip Capacitance の測定セットアップ                         | 24 |

| 3.4  | TypeA の 1 ストリップあたりのリーク電流の電圧依存性                                   | 25 |

| 3.5  | TypeB <b>の</b> 1ストリップあたりのリーク電流の電圧依存性                             | 25 |

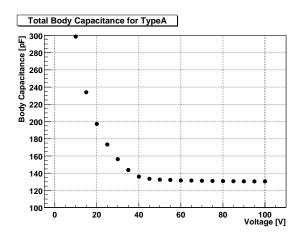

| 3.6  | TypeA の Total Body Capacitance の電圧依存性                            | 25 |

| 3.7  | TypeB のの Total Body Capacitance の電圧依存性                           | 25 |

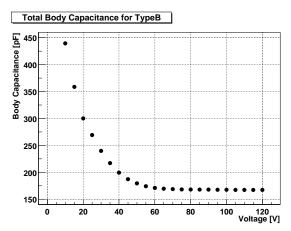

| 3.8  | TypeA <b>の</b> 1 ストリップあたりの Inter-strip Capacitance <b>の電圧依存性</b> | 26 |

| 3.9  | TypeB <b>の</b> 1 ストリップあたりの Inter-strip Capacitance の電圧依存性        | 26 |

| 3.10 | TypeA、TypeB を CP580K で読み出すときの回路図                                 | 27 |

| 3.11 | TypeA、TypeB を Single Channel で読み出したときの SSD のセットアッ                |    |

|      | プ。TypeA は両隣を GND に落とし、TypeB は読み出す両隣の上下のスト                        |    |

|      | リップを GND に落としてある。                                                | 27 |

| 3.12 | SSD と線源の位置関係                                                               | 28 |

|------|----------------------------------------------------------------------------|----|

| 3.13 | セットアップの写真                                                                  | 28 |

| 3.14 | 読み出すストリップの両隣のストリップを GND に落とした状態の TypeA                                     |    |

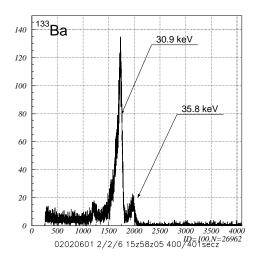

|      | で得られた <sup>133</sup> Ba <b>のスペクトル</b>                                      | 29 |

| 3.15 | 読み出すストリップの両隣のストリップを GND に落とした状態の TypeB                                     |    |

|      | 下側のストリップで得られた $^{133}{ m Ba}$ のスペクトル $\dots$                               | 29 |

| 3.16 | 読み出すストリップの両隣のストリップを GND に落とした状態の TypeB                                     |    |

|      | 上側のストリップで得られた <sup>133</sup> Ba のスペクトル                                     | 29 |

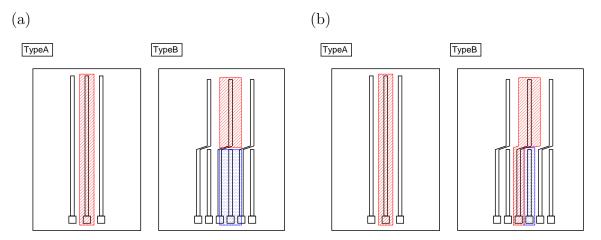

| 3.17 | (a) TypeA、TypeB の設計から予想される有効面積 (b)TypeA、TypeB で                            |    |

|      | 反応したイベント数から仮定した有効面積                                                        | 30 |

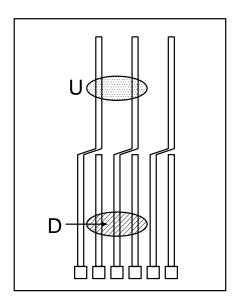

| 3.18 | コリメートした $X$ 線の照射領域。 $U$ は上側のストリップで $\mathrm{p}^+$ ストリップ                    |    |

|      | がある部分。 $D$ は上側のストリップで $p^+$ ストリップがない部分 (引き延ば                               |    |

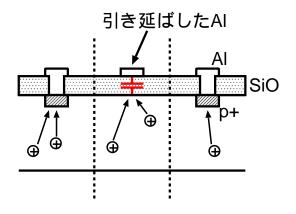

|      | された Al 電極部)                                                                | 31 |

| 3.19 | $\mathrm{TypeB}$ 上側の引き延ばされた $\mathrm{Al}$ 電極にコリメートした $\mathrm{X}$ 線を照射したと  |    |

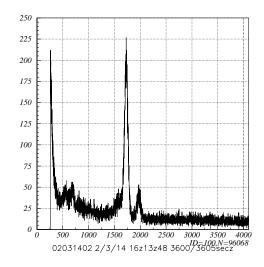

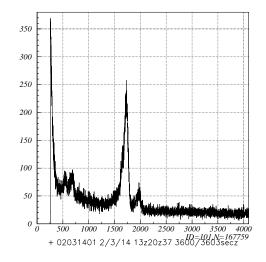

|      | きに得られたスペクトル                                                                | 32 |

| 3.20 | $\mathrm{TypeB}$ 上側の $\mathrm{p}^+$ ストリップにコリメートした $\mathrm{X}$ 線を照射したときに得ら |    |

|      | れたスペクトル                                                                    | 32 |

| 3.21 | TypeB の引き延ばされた Al 電極部 (図 3.19) とストリップ部 (図 3.20) のス                         |    |

|      | ペクトルの足し合わせ                                                                 | 32 |

| 3.22 | 引き延ばされた Al 電極が n バルクとコンデンサを形成している場合                                        | 32 |

| 3.23 | TypeB の Body Capacitance の構成                                               | 34 |

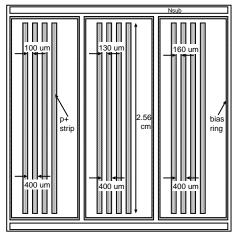

| 3.24 | Teststructure の設計                                                          | 35 |

|      | Teststructure の写真                                                          | 35 |

| 3.26 | ストリップギャップと電束密度の相関                                                          | 36 |

| 3.27 | 3 種類の DSSD のリーク電流の比較                                                       | 37 |

| 3.28 | 3種類の DSSD の Total Body Capacitance の比較                                     | 37 |

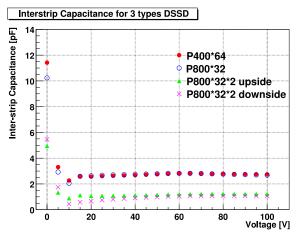

|      | 3 種類の DSSD の Inter-strip Capacitance(p <sup>+</sup> ストリップ) の比較             | 37 |

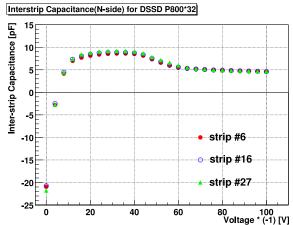

|      | DSSD P800×32のn <sup>+</sup> ストリップのInter-strip Capacitance                  |    |

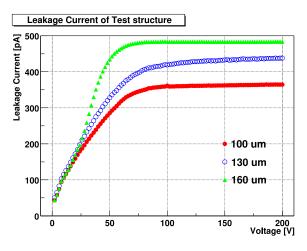

|      | Test structure のリーク電流の電圧依存性                                                |    |

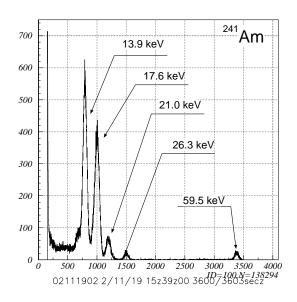

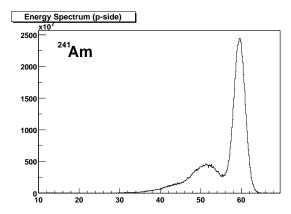

|      | DSSD P400×64 で得られた $^{241}$ Am のエネルギースペクトル                                 |    |

|      | $\mathrm{RC}$ チップ $(200~\mu\mathrm{m}$ ピッチ) の写真 $\ldots$                   |    |

|      | SSD、RC チップ、CSA の接続方法                                                       |    |

|      | RC チップ全体のリーク電流                                                             |    |

|      | RC チップ全体の Body Capacitance                                                 |    |

|      | RC チップの 1 ストリップあたりの Inter-strip Capacitancek                               |    |

| 3.38 | $RC$ チップを用いた $TypeA$ で測定した $^{133}Ba$ のエネルギースペクトル                          | 42 |

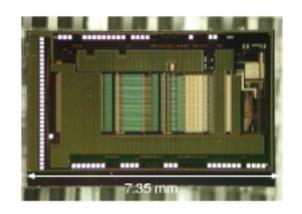

|      | VA32TA <b>チップの</b> 写真                                                      |    |

| 4.2  | VA32TA <b>のブロックダイアグラム</b>                                                  | 45 |

| 43   | Majority selection module の概要                                              | 46 |

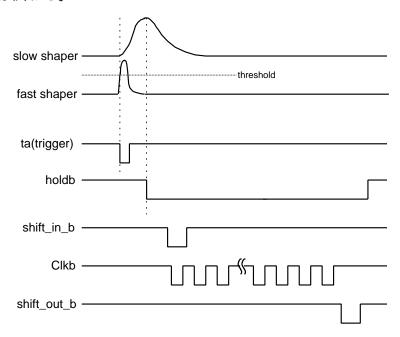

| 4.4  | VA32TA の読み出しタイミングチャート                                                                            | 49 |

|------|--------------------------------------------------------------------------------------------------|----|

| 4.5  | フロントエンドカードの写真                                                                                    | 50 |

| 4.6  | FEC の回路設計                                                                                        | 51 |

| 4.7  | VA-DAQ の写真                                                                                       | 52 |

| 4.8  | 新しい読み出しシステムのダイアグラム                                                                               | 53 |

| 4.9  | バイアスボードの写真                                                                                       | 54 |

| 4.10 | IFC の写真。左図が ROC と接続する基板。右図は 16 個の 34 ピン half-pitch                                               |    |

|      | コネクタが並んでおり、FEC と接続する基板                                                                           | 55 |

| 4.11 | ROC の写真                                                                                          | 55 |

| 4.12 | $16$ 枚の FEC からのデータを読み出すときのタイミングチャート $\dots$                                                      | 56 |

| 5.1  | Test structure の複数チャンネル同時計測のためのセットアップ                                                            | 59 |

| 5.2  | AC 結合モジュール (左図) と $DC$ 結合モジュール (右図)                                                              | 59 |

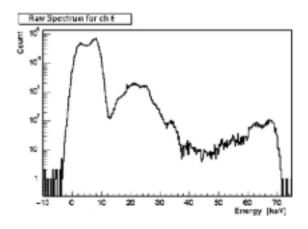

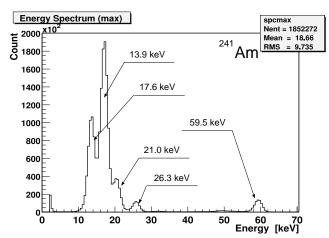

| 5.3  | 得られたデータをそのまま用いたときの $^{241}\mathrm{Am}$ のエネルギースペクトル                                               | 60 |

| 5.4  | 一連のデータ解析をした後のエネルギースペクトル                                                                          | 60 |

| 5.5  | AC 結合モジュールのチャンネルとエネルギー分解能の関係                                                                     | 61 |

| 5.6  | ${ m AC}$ 結合モジュールを用いた ${ m ^{241}Am}$ の複数チャンネル加算スペクトル。測                                          |    |

|      | 定条件は温度 $20$ 度、 $shaping time = 2 \mu sec$                                                        | 61 |

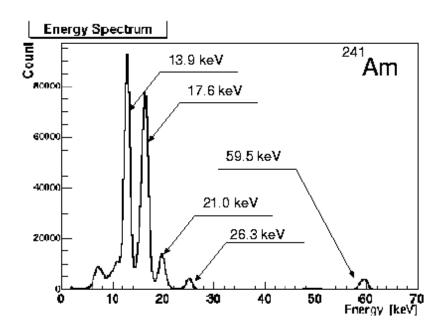

| 5.7  | ${ m DC}$ 結合モジュールを用いた $^{241}{ m Am}$ の複数チャンネル加算スペクトル。測                                          |    |

|      | 定条件は温度 $0$ 度、 $\mathrm{shaping\ time} = 4~\mu\mathrm{sec}$                                       | 62 |

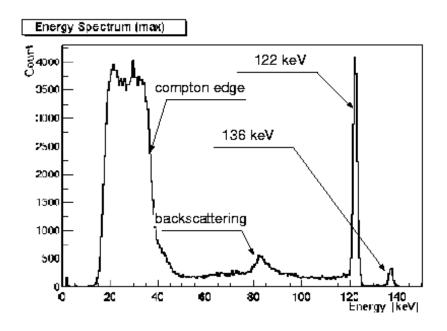

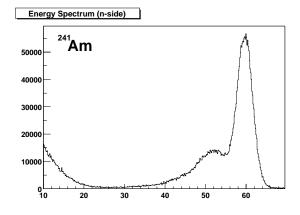

| 5.8  | $ m DC$ 結合モジュールを用いた $^{57}Co$ の複数チャンネル加算スペクトル。測定                                                 |    |

|      | 条件は温度 $0$ 度、 $\mathrm{shaping\ time} = 4~\mu\mathrm{sec}$                                        | 63 |

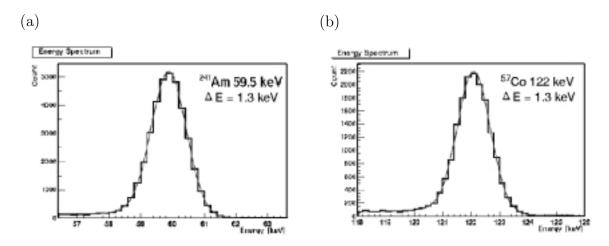

| 5.9  | DC 結合モジュール、温度 $0$ 度、 $\mathrm{shaping\ time} = 4\ \mu\mathrm{sec}$ で得られた $^{241}\mathrm{Am}59.5$ |    |

|      | ${ m keV}$ のとフィッティング結果 ${ m (a)}$ と ${ m ^{57}Co122}$ ${ m keV}$ のフィッティング結果 ${ m (b)}$ .         | 63 |

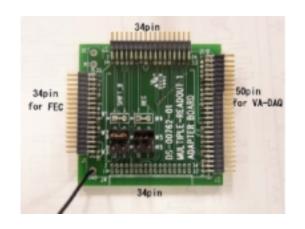

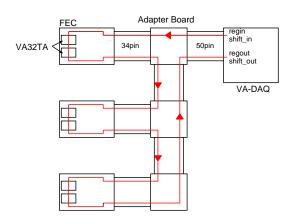

| 6.1  | 複数の FEC を 1 つの VA-DAQ で制御するためのアダプターボード                                                           | 65 |

| 6.2  | アダプターボードを用いた読み出しの概念図                                                                             | 65 |

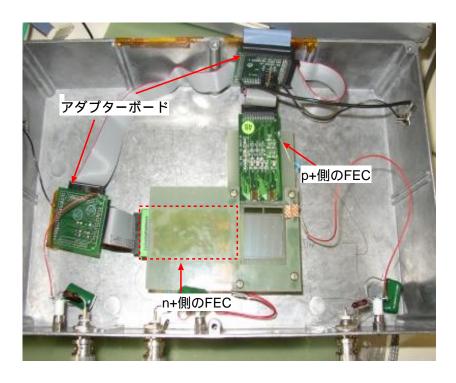

| 6.3  | DSSD の両面同時読み出しのためのセットアップ                                                                         | 66 |

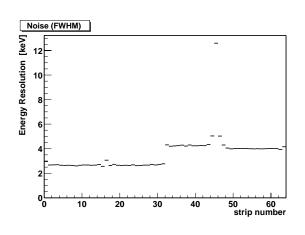

| 6.4  | 各ストリップで得られたノイズの大きさ。チャンネル番号 $0 \sim 31$ が $p^+$ 側の                                                |    |

|      | ストリップであり、 $32\sim63$ が $\mathrm{n}^+$ 側のストリップ。 $$                                                | 66 |

| 6.5  | $	ext{DSSD}$ の両面同時読み出しで得られた $	ext{p}^+$ 側の多チャンネル加算スペクト                                           |    |

|      | ル。測定条件は $^{241}$ Am、peaking time = $2 \mu sec$                                                   | 66 |

| 6.6  | $	ext{DSSD}$ の両面同時読み出しで得られた $	ext{n}^+$ 側の多チャンネル加算スペクト                                           |    |

|      | ル。測定条件は $^{241}$ Am、peaking time = $2 \mu sec$                                                   | 67 |

| 6.7  | $	ext{DSSD}$ の両面同時読み出しで得られた $	ext{p}^+$ 側の多チャンネル加算スペクト                                           |    |

|      | ル。測定条件は $^{57}$ Co、peaking time = $2 \mu sec$                                                    | 67 |

| 6.8  | DSSD のフラットイメージ                                                                                   | 68 |

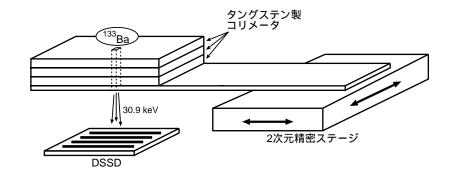

| 6.9  | コリメートした $X$ 線を $2$ 次元精密ステージを用いて測定するときのセット                                                        |    |

|      | アップ図                                                                                             | 60 |

| 6.10 | タングステン製のコリメータ。中心に 1 mm×1 mm の正方形の穴があいて                                    |    |

|------|---------------------------------------------------------------------------|----|

|      | いる。                                                                       | 69 |

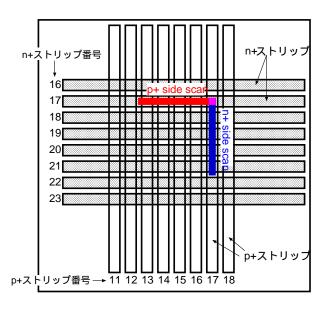

| 6.11 | コリメートした $X$ 線の照射位置。赤いラインが $\mathrm{p}^+$ 側をスキャンしたとき                       |    |

|      | の照射位置。青いラインが $\mathrm{n}^+$ 側をスキャンしたときの照射位置。                              | 69 |

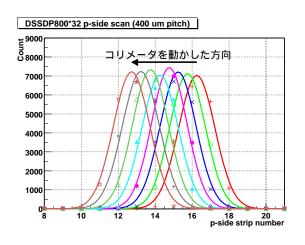

| 6.12 | $\mathrm{p}^+$ ストリップに対して垂直にコリメータを移動させたときの各ストリップ                           |    |

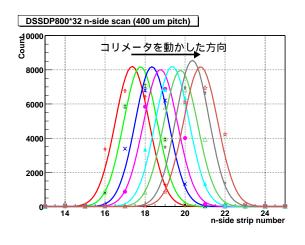

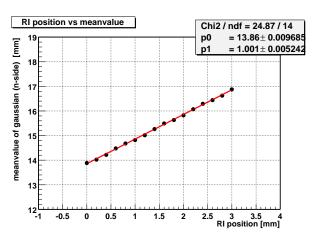

|      | のイベント数                                                                    | 70 |

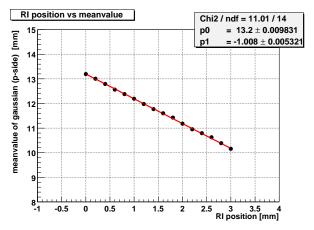

| 6.13 | p <sup>+</sup> ストリップのイベント数をガウス分布でフィッティングしたときの平均                           |    |

|      | 値 (線源の位置) とコリメータの移動距離の相関                                                  | 70 |

| 6.14 | $\mathrm{n}^+$ ストリップに対して垂直にコリメータを移動させたときの各ストリップ                           |    |

|      | のイベント数                                                                    | 70 |

| 6.15 | $\mathrm{n}^+$ ストリップのイベント数をガウス分布でフィッティングしたときの平均                           |    |

|      | 値 (線源の位置) とコリメータの移動距離の相関                                                  | 70 |

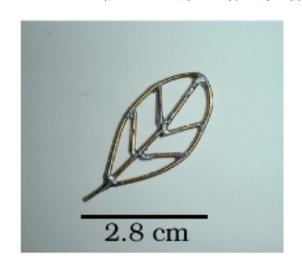

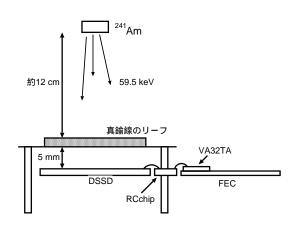

| 6.16 | 直径 $800~\mu\mathrm{m}$ の真鍮線で製作したリーフ $\ldots$                              | 71 |

| 6.17 | 真鍮線のリーフを撮像するときのセットアップ図                                                    | 71 |

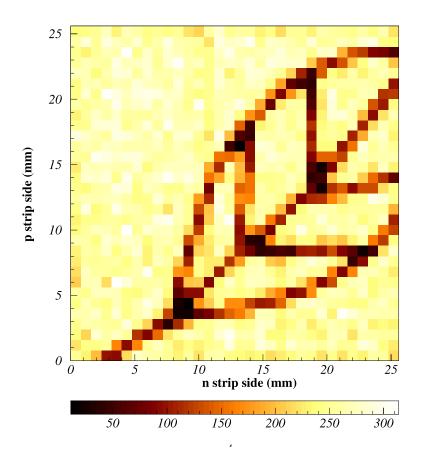

| 6.18 | 真鍮線のリーフの撮像結果                                                              | 72 |

| 6.19 | スプリットイベントの概念図                                                             | 72 |

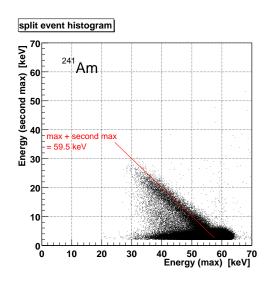

| 6.20 | 最も大きい波高値と $2$ 番目に大きい波高値の $2$ 次元ヒストグラム。 $^{241}{ m Am}$ 、                  |    |

|      | peaking time = 2 $\mu$ sec                                                | 74 |

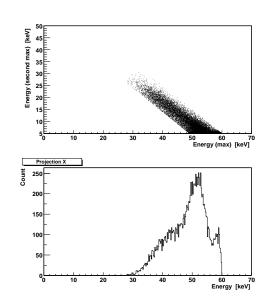

| 6.21 | スプリットイベントを抜き出した $2$ 次元ヒストグラム $(上)$ と上図の $X$ 軸へ                            |    |

|      | の射影 (下)                                                                   | 74 |

| 6.22 | 最も大きい波高値と $2$ 番目に大きい波高値の $2$ 次元ヒストグラム。 $^{57}{ m Co}$ 、                   |    |

|      | peaking time = 2 $\mu$ sec                                                | 75 |

| 6.23 | スプリットイベントを抜き出した $2$ 次元ヒストグラム $(上)$ と上図の $X$ 軸へ                            |    |

|      | の射影 (下)                                                                   | 75 |

| 6.24 | FEC と TypeA <b>の</b> 接続。下側が DC 結合、上側が AC 結合である。                           | 75 |

| 6.25 | 新しい読み出しシステムを用いて $\mathrm{TypeA}$ を読み出すときのセットアップ .                         | 75 |

| 6.26 | ${ m ROC}$ を用いて ${ m TypeA}$ 、 ${ m RC}$ チップ、 ${ m VA32TA}$ チップを読み出したときの多 |    |

|      | チャンネル加算スペクトル (AC 結合)                                                      | 76 |

| 6.27 | ${ m ROC}$ を用いて ${ m Type A}$ 、 ${ m VA32TA}$ チップを読み出したときの多チャンネル          |    |

|      | 加算スペクトル (DC 結合)                                                           | 76 |

# 表目次

| 3.1 | TypeA と TypeB の基本設計の比較                    | 23 |

|-----|-------------------------------------------|----|

| 3.2 | TypeA と TypeB 上下のエネルギー分解能と全体のカウントレートの比較 . | 28 |

| 3.3 | TypeA と TypeB 上下の基礎パラメータとエネルギー分解能         | 34 |

| 3.4 | DSSD <b>の基本設計の比較</b>                      | 35 |

| 4.1 | VA32TA <b>の基本仕様</b>                       | 45 |

| 5.1 | 実際に得られたエネルギー分解能と理論的に予想されるエネルギー分解能         |    |

|     | の比較                                       | 61 |

## 第1章 序論

### 1.1 X線ガンマ線天体物理学

1960年代以降、X線ガンマ線の観測衛星がいくつも打ち上げられ、宇宙のあらゆると ころでX線ガンマ線の放射を伴う高エネルギー現象を伴っていることがわかってきた。特 に、10 keV 以下のエネルギー領域では Newton 衛星 (1999 年、欧州) や Chandra 衛星 (1999 年、米国)によって今までにない感度と位置分解能で天体を観測することができている。 数 10 MeV 以上では EGRET 衛星 (1991 年、米国) がガンマ線天体物理学を飛躍的に向上 させ、2006 年打ち上げ予定の  $\mathrm{GLAST}$  衛星 (米国) によって数  $10~\mathrm{MeV}$  以上のガンマ線に 対して EGRET を 1 桁以上上回る感度を持つことが期待されている。図 1.1 に主な X 線ガ ンマ線観測衛星の感度を示す。この図からわかるように、数 10 keV から数 10 MeV のエ ネルギー領域に大きな Sensitivity gap がある。10 keV 以下のエネルギーでは反射望遠鏡 を利用した集光観測が可能であり、数 10 MeV 以上では電子陽電子対生成の飛跡を追うこ とにより高感度な観測ができる。これに対し、100 keV 以上、数 MeV 以下の領域ではコ ンプトン散乱が支配的になる。シンチレータを用いると、X線ガンマ線が検出器内でコン プトン散乱の後に光電吸収を行った場合のみ光子のエネルギーを測定することは可能であ る。しかし、光子が光電吸収をして全てのエネルギーを落とす前に検出器から逃げてしま う場合も多く、検出器の検出効率が低くなってしまう。さらにエネルギーを測るだけでは 光子の到来方向を知ることができない。

ところが、この Sensitivity gap になっているエネルギー領域は非常に重要な情報を多く含んでいる。超新星爆発やブラックホール、銀河団などから放射される高エネルギー粒子の加速機構は未だ解決されておらず、高エネルギー粒子が放出する X 線ガンマ線を観測することが重要である。 $10~{\rm keV}$  以下の領域では高温プラズマからの熱的放射が無視できないのに対して、 $10~{\rm keV}$  以上になると高エネルギー粒子からの非熱的放射が支配的となり、加速機構の解明には必要不可欠な観測領域である。また、このエネルギー領域には $^{57}{\rm Co}(122~{\rm keV})$ 、 $^{56}{\rm Ni}(158~{\rm keV}$ 、 $812~{\rm keV})$ 、 $^{22}{\rm Na}(511~{\rm keV}$ 、 $1275~{\rm keV})$ 、 $^{56}{\rm Co}(847~{\rm keV})$  などの多くの核ガンマ線が存在する。これらの元素は超新星爆発などで作られるため、銀河における星の生成過程を知る手がかりになる。

CGRO(Compton Gamma-Ray Observatory) に搭載された COMPTEL 衛星 (1991 年、米国) はこのエネルギー領域でコンプトン散乱の運動学を利用した最初の検出器であり、最初の散乱を位置検出型のシンチレータで測定し、次の光電吸収を二つ目のシンチレータで測定する。この方法により COMPTEL 衛星は上記のような科学的興味に対してさまざまな情報をもたらした。しかし、散乱した光子を吸収するための立体角が小さいため、

図 1.1: さまざまな観測衛星の感度の比較。横軸はX線、ガンマ線のエネルギー、縦軸は感度を表す。

検出効率が低く、エネルギー、位置決定精度が悪かったので角分解能も十分ではなく、感度が低かった。

よって、次世代の検出器として 100 keV 以上に高い感度を持ち、さらに高精度のエネルギー分解能を備えた検出器の開発が必要になってくる。その候補に挙げられているのが多重コンプトンガンマ線カメラである。

## 1.2 多重コンプトンガンマ線カメラ

1987年、釜江 (T.Kamae et al,1987) らによって多重コンプトンガンマ線カメラが提案されて以来、さまざまな検出器構成が提案、試作されている。シリコン半導体のみを用いたもの、シンチレータと組み合わせたもの、液体キセノンやゲルマニウム半導体を用いたものなどが挙げられる。これらに対し、我々のグループが開発を進めている多重コンプトンガンマ線カメラの特徴はシリコン (Si) 半導体とテルル化カドミウム (CdTe) 半導体をハイブリッドにし、極めて高いエネルギー分解能を達成することである。散乱体として、本論文で詳しく述べるシリコンストリップ検出器 (SSD:Silicon Strip Detector) と CdTe 半導体のピクセル検出器を多層に積み上げ、より高エネルギーなガンマ線に対する感度を上げるために吸収体として厚い CdTe で覆う。SSD は低エネルギー側で散乱効率が良く、大面積化が可能であるため、散乱体として極めて重要である。多重コンプトンガンマ線カメラの基本的な構造を図 1.2(a) に示す。

図 1.2: (a) 多重コンプトンガンマ線カメラの基本構造。散乱体として SSD、CdTe ピクセル検出器を用いる。天体からの X 線、ガンマ線は散乱体で複数回のコンプトン散乱を繰り返し、吸収体で光電吸収を起こす。(b) 数イベントの重ね合わせ。円弧が重なり合っているところが天体の位置になる。円弧の太さは検出器のエネルギー分解能に依存する。

多重コンプトンガンマ線カメラの検出原理はコンプトン散乱の運動学

$$\cos\phi_1 = 1 + \frac{m_e c^2}{E_1 + E_2 + E_3} - \frac{m_e c^2}{E_1 + E_2}$$

(1.1)

$$\cos\phi_2 = 1 + \frac{m_e c^2}{E_2 + E_3} - \frac{m_e c^2}{E_3}$$

(1.2)

を基にしている。 $\phi_1$ 、 $\phi_2$  はそれぞれ光子の1回目、2回目の散乱の散乱角、 $E_1$ 、 $E_2$ 、 $E_3$ はそれぞれ何度目かの散乱における反跳電子のエネルギーである。この式からわかるよう に、入射 X 線、ガンマ線の反応位置とそこで落としたエネルギーがわかれば、一つの光 子に対して、入射方向を一つのコーン上に制限することができる。それを複数イベント重 ね合わせることによって天体の位置を求めることができる(図1.2(b))。多重コンプトンガ ンマ線カメラの角分解能 (コーンの太さ) を決定するのは式 (1.1)、(1.2) からみてもわかる ように、検出器のエネルギー分解能である。コンプトン散乱を考えた場合、理想的な半導 体検出器と読み出し回路を仮定すると最も高いエネルギー分解能は Doppler Broadening によって決められる。Doppler Broadening とはコンプトン散乱で光子が落としたエネル ギーを測定する場合、反応する電子がランダムな運動量を持って原子核に束縛されてお り、反跳電子のエネルギーを完璧に測定できたとしても測定エネルギーが広がってしまう ことである。よって、我々はこの Doppler Broadening にせまったエネルギー分解能を持っ た検出器の開発を目指している。特に Doppler Broadening は原子番号が小さいほど影響 は少なく、シリコンは重い元素であるキセノンやゲルマニウム、CdTe に比べて高いエネ ルギー分解能を達成することができるので、多重コンプトンガンマ線カメラの角分解能向 上には欠かすことのできない検出器である。

多重コンプトンガンマ線カメラの原理を用いるとさまざまなメリットを生み出せる。初めに、高い感度が達成できることである。2層から多層にすることで反応率が上がると同時に、最初の二つの散乱の反応位置と落としたエネルギーと三回目の反応で落としたエネルギーがわかれば、検出器内で全てのエネルギーを落とさなかったとしても入射 X 線ガンマ線のエネルギーと到来方向を一意に決定することができるからである。これにより、コンプトン連続部をほとんど取り除くことができる。複数イベント集めることによって一つの光子に対して到来方向が決定できるので、天体以外からの X 線ガンマ線や、内在あるいは放射化バックグラウンドなどの徹底した除去が可能であり、バックグラウンドが支配的なガンマ線領域では大きな武器となる。さらに、コンパクトな設計が可能なため広い視野を持つ。明るいガンマ線天体の多くは時間変動が激しいので、できるだけ広い視野でモニタリングしていることが望ましい。

本論文では、多重コンプトンガンマ線カメラの散乱体となる SSD の基礎特性と撮像能力についてまとめる。2 章、3 章では SSD の基礎特性について述べ、4 章では複数チャンネル同時計測のための読みだしシステムについてまとめる。5 章では片面 SSD の複数チャンネル読みだし結果をまとめ、6 章では両面 SSD の性能評価と撮像能力について議論する。最後に今後の課題に触れる。

## 第2章 半導体検出器の基礎特性とシリコ ンストリップ検出器

#### 2.1 半導体を用いた放射線検出器の検出原理

放射線と物質の相互作用には光電効果、コンプトン散乱、電子陽電子対生成の3種類がある。放射線は物質中の束縛電子とこれらの相互作用を行い、そのエネルギーを束縛電子に渡す。エネルギーを得た電子は物質中を動き、飛跡に沿って電子ホール対を生成する。半導体を用いた放射線検出器の動作原理は、これらの電離作用により生成された電子ホール対を分離し、電極に収集して信号にすることである。生成された電子ホール対の数は反応した放射線のエネルギーに比例しているので、信号の大きさがそのまま放射線のエネルギーを表す。正しくエネルギーを知るためには、生成された電子ホール対が再結合する前に効率良く分離、収集しなければならず、そのためには半導体結晶内に電場をかけることが必要である。純粋なシリコン結晶の場合、バンドギャップは大きく(1.15 eV)、常温で熱励起によるキャリアがほとんど存在しないので結晶中に電場をかけることができる。しかし、実際のシリコン結晶は不純物を含んでいるので、熱励起されたキャリアを持っている。そこで、シリコン結晶を放射線検出器として使用する場合、結晶内からキャリアを消す「空乏化」が必要になり、空乏化された結晶内(空乏層)が有感領域となる。シリコン検出器は極めて純粋な結晶を用い、ダイオード構造にして逆バイアスをかけることによって空乏層を厚くしている。

## 2.2 pn 接合ダイオード

シリコンやゲルマニウムは 4 価の原子なので、5 価のリンを小量混ぜるとリンに置き換わった格子で電子が一つ余り、容易に伝導電子となって、電子をキャリアとする n 型半導体を作ることができる。逆に 3 価のホウ素を少量混ぜることにより、ホールをキャリアとする p 型半導体ができる。n 型、p 型半導体のバンドギャップ内にできる新しいエネルギーレベルの構造を図 2.1 に示す。ドープした不純物濃度が特に高いものを+ 記号をつけてそれぞれ  $n^+$  型、 $p^+$  型半導体という。この 2 つの半導体が金属学的に結合されると pn 接合ダイオードができる。接合近傍には大きなキャリア密度勾配ができるので、キャリアの拡散が起こり、n 型から p 型に向けて電子が移動し、p 型から n 型に向けてはホールが移動する。その結果、移動した電子ホールが再結合し、残されたアクセプタイオンとドナーイオンにより電場が作られる。この電場は n 型、p 型半導体のキャリアの侵入を防ぐ方向に

図 2.1: n型、p型半導体とpn接合のバンドギャップ内にできる新しいエネルギーレベル

作られるので、接合近傍はキャリアがほとんど存在しない空乏層になる。さらに、pn 接合ダイオードに逆バイアス電圧をかけることにより、それぞれのキャリアは接合部のポテンシャル壁を越えて再結合する。始めに中性であった n型、p 型半導体はそれぞれ正負に帯電し、逆バイアス電圧とつり合うところまでキャリアが取り除かれ、空乏層を広げることができる。

### 2.3 シリコンストリップ検出器の基礎

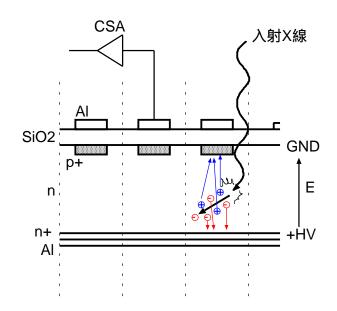

#### 2.3.1 シリコンストリップ検出器の構造

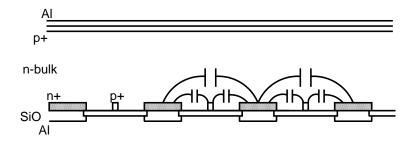

高エネルギー物理学の分野で短寿命粒子の検出のために、高い位置分解能を持つ飛跡検出器として開発されたのがシリコンストリップ検出器 (SSD:Silicon Strip Detector) である。SSD の基本的な構造は図 2.2 のように、n 型シリコンウェーハーの上に  $p^+$  型のシリコンを細い短冊状に並べ、多数の pn 接合ダイオードを形成したもので、それぞれのダイオードが独立な検出器として働く。抵抗を減らすために  $p^+$  ストリップ、 $backplane(n^+$  層) には Al 電極が取り付けられている。さらに  $p^+$  ストリップ側には絶縁層 ( $SiO_2$ ) を入れてカップリングコンデンサを形成し、直流電流が流れ込まないようにしている。

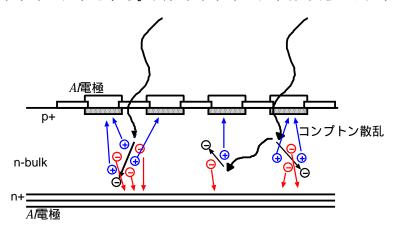

逆バイアスをかけて空乏層を広げた SSD に X 線が入射した場合を考える。図 2.2 のように、n バルク内で光電効果を起こした場合、エネルギーを得た電子がn バルク内を走り、その軌跡に沿って電子ホール対が生成される。生成された電子は電場に従って  $n^+$  側に引き寄せられるのに対し、ホールは最も近い  $p^+$  ストリップに引き寄せられる。つまり、電荷が集められて信号として読み出された  $p^+$  ストリップが X 線の反応位置を示すのである。

SSD の特徴としては、上で述べたように高い位置分解能を持つことの他に、高速応答性があげられる。厚さ  $300\mu$  m の典型的な SSD では deadtime は約 30 nsec であり、プラスチックシンチレータと同程度の速い応答をする。

図 2.2: シリコンストリップ検出器の基本構造。n バルク内で X 線が光電吸収を起こした場合、エネルギーに比例した電子ホール対ができ、内部電場に従って電極に収集される。

#### 2.3.2 Leakage Current

半導体では、熱的に励起された電子ホールがエネルギーギャップを越えて伝導帯に遷移することにより、直流電流が流れる。この電流をリーク電流をいう。純粋な半導体の場合、リーク電流はこの熱励起による成分のみであり、ドナー、アクセプタがドープされた結晶でも空乏層を形成していれば同じである。しかし、実際の結晶は完全なものではなく、必ず有限の欠陥やドナー、アクセプタ以外の不純物を含んでいる。これらがエネルギーギャップに新たなエネルギーレベルを作り、電子ホールの伝導帯への遷移を助けてリーク電流を作り出す。SSD の場合、複雑な構造をしているため、結晶内に存在する不純物以外によるリーク電流も存在する。ダイオード構造、絶縁層や電極などがシリコン結晶を乱し、それらによる欠陥、不純物等のエネルギー準位によるリーク電流や、絶縁層など有限な抵抗から洩れ出すリーク電流がある。これらのリーク電流は SSD を製造する過程の質に大きく依存し、製造過程の質が高ければ n バルクからのリーク電流が支配的になり、質が悪ければ表面部分からのリーク電流が効いてくる。

リーク電流は温度にも大きく依存する。一般には

$$I(T) \propto T^2 exp(\frac{-E}{2k_BT})$$

(2.1)

の形をしている。T は温度、E はエネルギーギャップ、 $k_B$  はボルツマン定数である。常温では 7.5 度で約 2 倍変化するので、室温から 0 度に冷却すればリーク電流を一桁落とせる。また、放射線損傷によってもリーク電流は増加する。放射線損傷は大きく分けてバルク損傷と表面損傷の二つがあり、特にバルク損傷がリーク電流の増加につながる。バルク損傷は結晶内の原子が放射線と相互作用し、本来の位置からずれて結晶が乱れることであ

る。表面損傷は表面の絶縁層に荷電粒子が通過することによるイオン化帯電効果である。 絶縁層で作られた電子、ホール、陽イオンのうち、電子は移動度が高いので拡散して消え るが、ホールと陽イオンは移動度が低いため欠陥などに容易にトラップされ、正電荷を蓄 積してしまう。

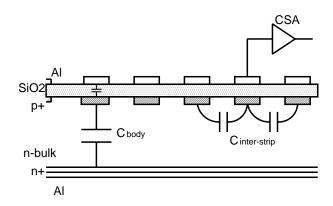

#### 2.3.3 Body Capacitance & Inter-strip Capacitance

SSD が持つ容量は主に p+strip と backplane 間で形成する Body Capacitance と、ある p+ ストリップとその周辺の p+ ストリップ間で形成する Inter-strip Capacitance がある (図 2.3)。一般的な pn 接合の場合、逆バイアスをかけなくても、数  $10~\mu m$  の空乏層が存在

☑ 2.3: Body Capacitance ∠ Interstrip Capacitance

し、逆バイアスをかけていくにつれて  $p^+$  ストリップ側から空乏層が広がる。それにつれて Body Capacitance も徐々に減っていき、完全に空乏化できると Body Capacitance は一定値をとる。よって、Body Capacitance を測定すれば全空乏化電圧を知ることができる。理論的には全空乏化電圧は

$$V_n = \left(\frac{d}{0.53}\right)^2 \frac{1}{\rho_n}$$

(バルクが n 型の場合) (2.2)

$$V_n = (\frac{d}{0.32})^2 \frac{1}{\rho_p}$$

(バルクが p 型の場合) (2.3)

で表すことができ、d は SSD の厚さ、 $\rho_n$ 、 $\rho_p$  はそれぞれ n 型、p 型半導体の比抵抗である。これからわかるように、同じ比抵抗のバルクを持つ検出器でも n 型か p 型かにより全空乏化電圧が異なる。これは電子とホールの移動度の違いからきている。

Inter-strip Capacitance の場合も同じことがいえる。逆バイアスをかけていくと、空乏層が p<sup>+</sup> ストリップ側から広がっていくにつれて容量は減っていき、隣のストリップが形成している空乏層と結び付いたところで、一定値をとる。そのときの電圧は SSD の構造にも依るが、一般的な SSD の場合、全空乏化電圧よりも小さい。Inter-strip Capacitance は最も近い両隣のストリップからの寄与のみを測定するだけで、十分良い近似となる。

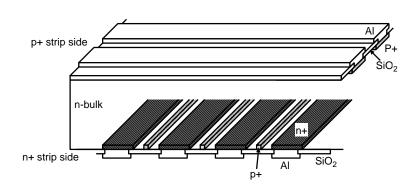

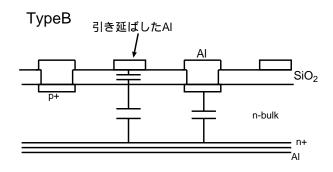

#### 2.3.4 両面シリコンストリップの構造

$p^+$  側だけがストリップ構造になっているものを片面シリコンストリップ検出器という。 片面 SSD の場合、放射線との相互作用により生成されたホールが最も近い $p^+$  ストリップ に収集されるので、1 次元の位置情報を知ることができる。電子は backplane に収集され、 位置情報には関与しない。これに対し、 $p^+$  側だけでなく $p^+$  ストリップに垂直な方向に $n^+$ 側がストリップ構造を形成しているものを両面シリコンストリップ検出器 (Double-sided Silicon Strip Detector:DSSD) という。DSSD の基本構造を図 2.4 に示す。生成されたホー ルは片面 SSD の場合と同様に最も近い $p^+$  ストリップに収集され、電子は最も近い $n^+$  ストリップに収集される。これにより、放射線の反応位置を 2 次元で知ることができる。

図 2.4: 両面シリコンストリップ検出器の基本構造

絶縁層  $(SiO_2 \ Periodical Perio$

$n^+$  ストリップ側の Inter-strip Capacitance は独立性を高めるための  $p^+$  ストリップ構造があるため、 $p^+$  側と少し異なる。図 2.5 のように両隣の  $n^+$  ストリップとで形成するキャパシタンスだけでなく、 $p^+$  ストリップとの間でもキャパシタンスを形成するので、 $p^+$  側の Inter-strip Capacitance よりも少し大きくなる。そのため、 $p^+$  ストリップ側に比べて $n^+$  ストリップ側の方がエネルギー分解能が悪くなる。

多重コンプトンガンマ線カメラを考えた場合、X 線ガンマ線の散乱位置を 2 次元で知る必要があるので、散乱体のシリコンストリップ検出器は DSSD でなければならない。また、高精度のエネルギー分解能が求められるので、反応した X 線ガンマ線が落としたエネルギーはエネルギー分解能が良い  $p^+$  ストリップ側で測り、 $n^+$  ストリップ側は位置情報

図 2.5: n<sup>+</sup> ストリップの Inter-strip Capacitance

を知るためだけに用いることになる。

## 2.4 シリコンストリップ検出器の読み出し

#### 2.4.1 半導体検出器の信号処理

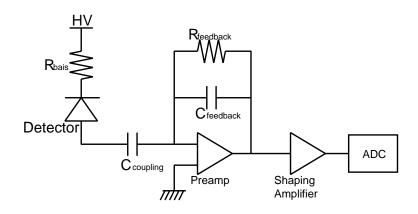

半導体検出器で電極に収集されたキャリアを信号として処理するために、一般には電荷有感型前置増幅器 (CSA:Charge Sensitive Amplifier) と波形整形増幅器、アナログデジタル変換器 (ADC:Analogue Digital Convertor) を用いる。まず、収集されたキャリアは CSA のフィードバックキャパシタンスに反比例した電圧値に変換される。次に整形増幅器で波形を整形、増幅し、その波高値を ADC でデジタル値にする。一般的な回路図を図 2.6 に示す。

図 2.6: 半導体検出器の一般的な信号処理回路図

SSD の場合、リーク電流が CSA のフィードバック抵抗に流れ込むのを防ぐために、SSD と CSA の間にカップリングコンデンサを入れてリーク電流をカットする必要がある。ただし、カップリングコンデンサの容量を信号に対して十分大きくしておかないと AC 結合によるカップリング損失を生み、エネルギー分解能が悪くなってしまう。また、動作温度を十分下げ、リーク電流が無視できる程度の大きさになればカップリングコンデンサを介

#### 2.4.2 シリコンストリップ検出器のエネルギー分解能

半導体検出器のエネルギー分解能は、放射線が検出器内でエネルギーEを失った場合、生成された電子ホールの数 n  $(=\frac{E}{\varepsilon})$  の統計分散に依存する。 $\varepsilon$  は電子ホール対を生成するために必要な平均エネルギーであり、シリコンの場合  $\varepsilon$ =3.65~eV である。バンドギャップよりも大きいのは、放射線と相互作用を起こした電子がシリコン内を通るときのエネルギー損失が、電子ホールを作る以外に原子核とのクーロン相互作用などで消費されるためである。電子ホール対が生じる事象がすべて独立である場合、生成される電子ホール数はポアソン分布に従い、分散はn になる。そのため、同じエネルギーが付与された場合でも $\varepsilon$  が小さな物質の方がエネルギー分解能がよい。しかし、実際の半導体検出器のエネルギー分解能はポアソン分布から予想される統計精度よりも良い値を示す。このポアソン分布からのずれを定量化するために導入されたのがファノ因子F であり、

$$F \equiv \frac{統計分散の観測値}{n} \tag{2.4}$$

で定義され、シリコンの場合ファノ因子は約0.1である。

半導体検出器からの信号を実際に読み出す場合、ファノ因子を考慮した統計分散の他に さまざまな電子回路ノイズの影響をうける。電子回路ノイズは主に以下の3種類ある。

#### 1. ジョンソンノイズ

抵抗などでキャリアの熱運動による揺らぎにより素子の両端に現れるノイズ。CSA に電荷 Q が入力される場合を考えると、コンデンサにかかる電圧とバイアス抵抗にかかる電圧  $V_R$  は等しいので、抵抗を流れるノイズ電流を  $I_n$  とすると

$$Q^{2} = \frac{(R_{bias}C)^{2}}{1 + (R_{bias}C\omega)^{2}}I_{n}^{2}$$

(2.5)

が成り立つ。よって、Q に対する  $I_n$  の伝達関数: $T(\omega)$  は

$$T_{bias}(\omega)^2 = \frac{(RC)^2}{1 + (RC\omega)^2}$$

(2.6)

となる。この式から伝達関数は、R が十分大きい場合、 $\propto \omega^{-2}$  となり、R が小さいと  $\propto RC^2$  になる。また、shaping Amplifier は CR-RC の組合せであり、その伝達関数は shaping time を  $\tau$  とすると

$$T(\omega) = \frac{(\omega\tau)^2}{1 + (\omega\tau)^2} \tag{2.7}$$

である。ノイズは全ての周波数に含まれているので、ENC(Equivarent Noise Chage) への寄与は

$$ENC_{bias} = \frac{1}{2\pi} \frac{1}{q_e^2} \int_0^\infty T(\omega)^2 T_{bias}(\omega)^2 I_n^2 d\omega$$

(2.8)

で表される。ジョンソンノイズの場合、「』は

$$I_n = \frac{4k_BT}{R_{bias}} \tag{2.9}$$

である  $(q_e$  は電気素量  $(\approx 1.6 \times 10^{-19} \ C)$ 、 $k_B$  はボルツマン定数、T は温度)。 計算すると、R が十分大きい場合は、

$$ENC_{bias} = 770 \sqrt{\frac{\tau \ (\mu \text{sec})}{R_{bias} \ (\text{M}\Omega)}}$$

(e<sup>-</sup>) (2.10)

Rが小さい場合は

$$ENC_{bias} = 0.77C(pF) \sqrt{\frac{R_{bias} (M\Omega)}{\tau (\mu sec)}}$$

(e<sup>-</sup>) (2.11)

となる。このことから、バイアス抵抗は極端に大きい、もしくは極端に小さいと ENC が 0 に近付くことがわかる。

#### 2. ショットノイズ

半導体検出器のリーク電流  $I_{lc}$  によって生じるノイズ。この場合もジョンソンノイズ と同じ式が使えるが、 $I_n$  が異なり、

$$I_n = \frac{e}{2q_e} \sqrt{q_e I_{lc} \tau} \tag{2.12}$$

で表すことができる。 ${

m e}$  は自然対数 (pprox 2.7183) である。 ${

m RC}$  の十分大きなシステムでは

$$ENC_{lc} = 110\sqrt{I_{lc}\tau \text{ (nA} \cdot \mu \text{sec)}}$$

(e<sup>-</sup>) (2.13)

となる。

#### 3. アンプノイズ

検出器が持つ電気容量に依存する CSA のノイズで、以下の式で表すことができる。

$$ENC_{amp} = k_0 + k_1 C_l (2.14)$$

$C_l$  は CSA にロードされる電気容量、 $k_0$ 、 $k_1$  は CSA と shaping amplifier によって決まる定数である。 $C_l$  は基本的に検出器が持つ電気容量と等しく、SSD の場合、Body Capacitance と Inter-strip Capacitance の足し合わせである。SSD と CSA が AC 結合されているときは、直列につながったカップリングコンデンサの容量も CSA にロードされるが、一般的にカップリングコンデンサの容量は Body Capacitance、Inter-strip Capacitance よりも十分大きく、電荷のゆらぎにはほとんど影響しない。

よって、これらのノイズを合成すると、

$$ENC_{total}^2 = ENC_{bias}^2 + ENC_{lc}^2 + ENC_{amp}^2$$

(2.15)

となる。半導体検出器のエネルギー分解能は  $\mathrm{ENC}_{totla}$  と統計揺らぎ  $\mathrm{ENC}_{stat}$  に依存し、一般に半値幅  $(\mathrm{FWHM})$  で表す。よって、半導体検出器のエネルギー分解能は

$$\Delta E(\text{FWHM}) = 2.35\varepsilon\sqrt{\left(F \cdot \frac{E}{\varepsilon}\right) + ENC_{total}^2}$$

(2.16)

で表すことができる。

## 第3章 シリコンストリップ検出器の性能 評価

#### 3.1 エネルギー分解能を上げるための工夫

シリコンストリップ検出器 (SSD) は典型的に数  $nA/cm^2$  のリーク電流を持っており、電荷有感型前置増幅器 (CSA) に接続する前にこの直流成分をカットしなければならない。そこで、SSD と CSA の間に AC カップル用のコンデンサを介する必要がある。

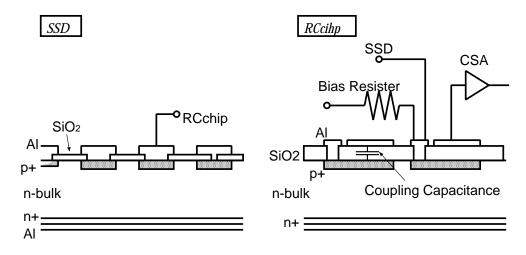

次世代ガンマ線衛星 GLAST で用いられているような今までの SSD は図 2.2 に示すように SSD とカップリングコンデンサ、各ストリップに独立にバイアス電圧を供給するバイアス抵抗がひとつのシリコンチップ上に作り込まれていた。しかし、今回我々のグループが多重コンプトンカメラの基礎研究用に試作した SSD は、歩留まりの向上、さらにはバイアス抵抗値を大きくするために SSD とは分離して、カップリングコンデンサ、バイアス抵抗を RCchip として別のシリコンチップ上に作った (図 3.1)。バイアス抵抗を大きくすることによってジョンソンノイズを減らすことができ、エネルギー分解能向上につながる。

図 3.1: 多重コンプトンガンマ線カメラの基礎研究用に製作した SSD と RCchip

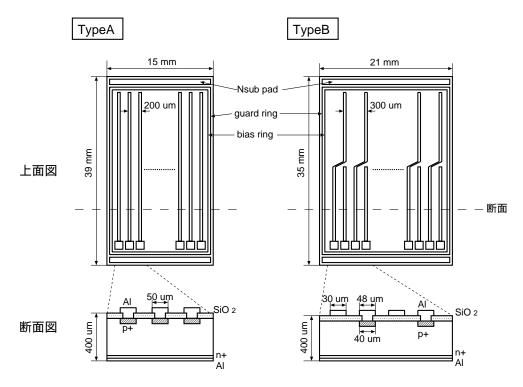

さらに、SSD のエネルギー分解能は SSD の容量に大きく影響されている。そこで我々のグループは通常のストリップ構造をしている SSD(TypeA) と、TypeA のストリップを垂直に 2 等分した TypeB を製作した。それぞれの構造を図 3.2 に示す。2 等分したため、

図 3.2: TypeA、TypeB の上面図と断面図

TypeB はボンディングパッドが付いているストリップと付いていないストリップができる (以後それぞれを下側のストリップ、上側のストリップと呼ぶ)。そこで、上側のストリップは図 3.2 のように Am 電極だけを引き延ばしてボンディングパッドをつけた。 TypeA、 TypeB のチップの大きさはそれぞれ 15  $mm \times 35 mm$ 、21  $mm \times 35$  mm であり、厚さはとも に 0.4 mm である。 TypeA と TypeB の基本設計を表 3.1 にまとめる。 TypeB は読みだし ストリップ数が 2 倍になるが、リーク電流と Body Capacitance、 Inter-strip Capacitance が半分になるのでエネルギー分解能の向上が期待できる。 TypeA、 TypeB にはストリップの他に以下のような構造がある。

#### 1. Nsub

シリコンチップの空乏層化していないエッジ部分を通して backplane と導通しているパッド。このパッドを用いると、SSD の  $p^+$  ストリップ面から backplane に電圧をかけることができる。

#### 2. バイアスリング

バイアスリングの外側で発生するリーク電流を吸収し、内部にあるストリップに外からリーク電流が流れ込むのを防ぐとともに、ストリップ周辺の電界を一様に整える作用をする。

#### 3. ガードリング

電気的に浮いている  $p^+$  をバイアスリングの周囲にめぐらせることで、バイアスリングの  $p^+$  部分周辺の電束密度が大きくならないようににする。

表 3.1: TypeA と TypeB の基本設計の比較

| SSD                     | TypeA               | TypeB                 |

|-------------------------|---------------------|-----------------------|

| ストリップ数                  | 64 本                | 64×2 <b>本</b>         |

| ストリップ間隔                 | $200~\mu\mathrm{m}$ | $300 \ \mu {\rm m}$   |

| ストリップの長さ                | 3.8 cm              | $1.7~\mathrm{cm}$     |

| p <sup>+</sup> ストリップの太さ | $40~\mu\mathrm{m}$  | $40~\mu\mathrm{m}$    |

| Al 電極の太さ                | $48~\mu\mathrm{m}$  | $48 \ \mu \mathrm{m}$ |

| 引き延ばした Al 電極の太さ         |                     | $30 \ \mu \mathrm{m}$ |

#### 3.2 I-V curve, C-V curve

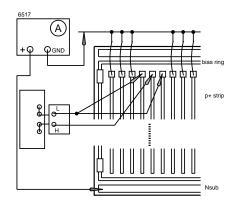

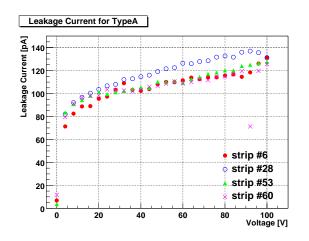

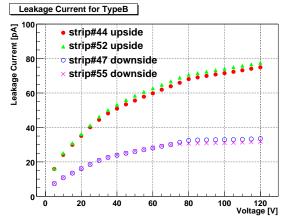

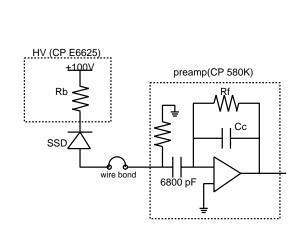

$\S 2.4.2$  で述べたように、SSD のエネルギー分解能を決める基本物理量はリーク電流とBody Capacitance、Inter-strip Capacitance である。そこで、まず TypeA に対して、1 ストリップあたりのそれぞれの値を測定した。リーク電流の測定セットアップを図 3.3 に示す。Nsub に正のバイアス電圧をかけ、読み出すストリップ以外のすべてのストリップとバイアスリングを GND に落とす。電源は Keithley Instruments 社製の Model 6517 を用いて 0 V から 100 V まで 4 V ステップで電圧をかけた。この電源は電流計を内蔵しており、電圧をかけると同時に電流を測定することができる。測定したときの温度は約 20 度で、測定したストリップは無作為に選び、6 番、28 番、53 番、60 番とした。得られた結果を図 3.4 に示す。この結果より、TypeA はバイアス電圧が 100 V のときに 1 ストリップあたり約 130 pA のリーク電流が流れていることがわかった。次に Body Capacitance を測定するときのセットアップを図 3.3(b) に示す。リーク電流測定と同様 Nsub から逆バイアスをかけ、全てのストリップを Cu テープにワイヤボンドした。キャパシタンスメータは HP 社製 Model 4284A を用いている。測定結果(図 3.6)は TypeA 全体で約 TypeA をであり、TypeA を平行板コンデンサと近似した場合、容量は

$$C = \varepsilon_{si}\varepsilon_0 \frac{S}{d} \tag{3.1}$$

で計算することができる。 $\varepsilon$   $_{si}$  はシリコンの比誘電率 (= 11.9)、 $\varepsilon$   $_{0}$  は真空の誘電率 (= 8.85×10 $^{-12}$  [F/m])、S はチップの面積、d は SSD の厚さに相当する。これを用いて計算すると、TypeA 全体の Body Capacitance は約 140 pF と計算され、実測値と約 7 %以内で一致している。Inter-strip Capacitance 測定のセットアップは図 3.3(c) の通りである。Nsubから逆バイアスをかけ、測定するストリップとその両隣のストリップ以外を GND に落とし、2 本以上隣のストリップからの寄与は測定されないようになっている。測定結果は 1 ストリップあたり 1.9 pF であることがわかった (図 3.8)。Inter-strip Capacitance は Body Capacitance に比べて低い電圧で一定の値をとっている。これは空乏層が  $p^+$  ストリップと n バルク境界から生成され、ストリップ間はすぐに全空乏層化されるためである。

次に TypeB のリーク電流、Body Capacitance、Inter-strip Capacitance を測定した。そ

(c)

図 3.3: (a) リーク電流の測定セットアップ (b)Body Capacitance の測定セットアップ (c)Inter-strip Capacitance の測定セットアップ

れぞれの測定セットアップは基本的に TypeA と同じ図 3.3 である。ただし、上側のストリップを測定するときはそのすぐ下側のストリップも GND に落とし、下側のストリップを測定するときはすぐ上側のストリップも GND に落としている。測定時の温度は約 20 度、測定したストリップの結果をそれぞれ図 3.5、図 3.7、図 3.9 に示す。 100V でのリーク電流は上側のストリップで約 70 pA、下側のストリップで約 35 pA となった。予想では同じ程度になるが、2 倍近く異なる結果になった。この結果についての考察は後節で行う。Body Capacitance は全体で約 170 pF となった。 TypeB を平行板コンデンサと仮定した場合、全体の Body Capacitance は約 180 pF と計算され、約 5 %以内で実測値と一致をしている。ただし、TypeB の 1 ストリップあたりの Body Capacitance については後節で考察する。Inter-strip Capacitance に関しては上側、下側ともに約 0.8 pF であるが、これは測定によって変動が大きく、あまり正確に測定することができなかったと思われる。

リーク電流の電圧依存性

図 3.4: TypeA の 1 ストリップあたりの 図 3.5: TypeB の 1 ストリップあたりの リーク電流の電圧依存性

図 3.6: TypeA の Total Body Capacitance の電圧依存性

図 3.7: TypeB のの Total Body Capacitance の電圧依存性

図 3.8: TypeA の 1 ストリップあたりの Inter-strip Capacitance の電圧依存性

図 3.9: TypeB の 1 ストリップあたりの Inter-strip Capacitance の電圧依存性

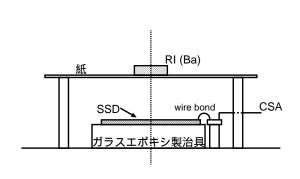

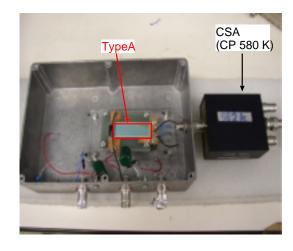

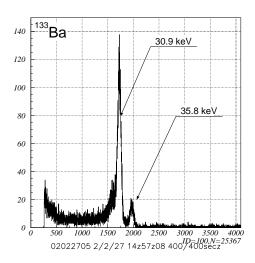

### 3.3 X線によるエネルギー分解能の測定

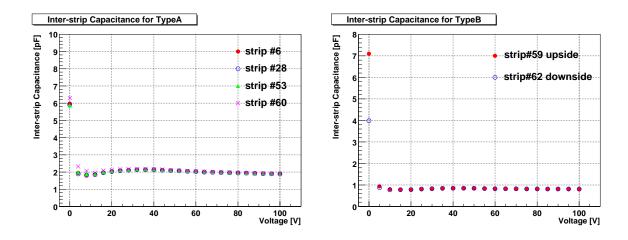

TypeA、TypeBにX線を照射し、1 ストリップの応答を単体 CSA、shaping amplifier を用いて読み込み、そのエネルギー分解能を比較する。はじめに、TypeA の性能評価をするために図 3.10 のような回路を組んだ。TypeA のひとつのストリップを基板にワイヤボンドし、導線を用いて AC 結合 CSA (Clear Pulse 社製 Model 580K) に信号を入力した。TypeA の Nsub に+100 V (Clear Pulse 社製 Model E6625) をかけ、読み出したストリップの両隣のストリップを GND に落とした (図 3.11)。 shaping amplifier の shaping time は  $2~\mu$ sec (ORTEC 社製 Model 571) とした。線源は 133 Ba( $30.9~\mu$ keV、 $35.0~\mu$ keV) を用い、図 3.12 のように SSD の真上にくるよう配置した。これらの測定は約 20 度で行った。TypeA、

図 3.10: TypeA、TypeB を CP580K で読み出すときの回路図

図 3.11: TypeA、TypeBをSingle Channel で読み出したときの SSD のセットアップ。 TypeA は両隣を GND に落とし、TypeB は 読み出す両隣の上下のストリップを GND に落としてある。

TypeB 上側、下側のストリップで得られたスペクトルの 30.9 keV のピークに対するエネルギー分解能とスレッショルドを超えたイベント全体のカウントレートを表 3.2 にまとめ、それぞれのエネルギースペクトルを図 3.14、図 3.15、図 3.16 に示す。ただし、TypeB 上側のストリップに関しては、ピークより低エネルギー側に大きな tail をひいているため、ピークの高エネルギー側を利用してガウス分布でフィッティングした結果であり、実際の分解能はもっと悪い。

得られたエネルギー分解能が TypeA、TypeB の構造から予想される値と一致するかどうかを確認する。TypeA の場合、§3.2 で測定したようにリーク電流は 130 pA、Body Capacitance、Inter-strip Capacitance はそれぞれ 2.0 pF、1.9 pF であった。さらに、今回使用した CSA はノイズの容量勾配を測定したところ、

$$ENC_{amp} = 100 + 2.1C(pF)$$

(e<sup>-</sup>) (3.2)

表 3.2: TypeA と TypeB 上下のエネルギー分解能と全体のカウントレートの比較

| SSD      | $\Delta E(FWHM)$ | count rate            |

|----------|------------------|-----------------------|

| TypeA    | 1.39  keV        | $157 \ {\rm s}^{-1}$  |

| TypeB 上側 | 1.28  keV        | $198 \ {\rm s}^{-1}$  |

| TypeB 下側 | 1.24  keV        | $64.2 \text{ s}^{-1}$ |

図 3.12: SSD と線源の位置関係

図 3.13: セットアップの写真

であることがわかった。これを基に式 2.10 から式 2.16 に代入していくと、 $\mathrm{ENC}_{lc}=56$   $(\mathrm{e}^-)$ 、 $\mathrm{ENC}_{amp}=110$   $(\mathrm{e}^-)$  となる。これより  $\Delta\mathrm{E}$   $(\mathrm{FWHM})=1.1$  keV になる。実際に得られたエネルギー分解能の値は 1.39 keV であり、少しノイズが大きいが、近い値と言える。

30.9 keV

図 3.14: 読み出すストリップの両隣のストリップを GND に落とした状態の TypeA で得られた  $^{133}$ Ba のスペクトル

図 3.15: 読み出すストリップの両隣のストリップを GND に落とした状態の TypeB 下側のストリップで得られた  $^{133}$ Ba のスペクトル

図 3.16: 読み出すストリップの両隣のストリップを GND に落とした状態の TypeB 上側のストリップで得られた  $^{133}$ Ba のスペクトル

## 3.4 1ストリップあたりの X 線検出領域

表 3.2 を見てわかるように、TypeA、TypeB 上下のストリップでカウントレートが大きく異なる。TypeA、TypeB の設計を考えると、それぞれのストリップの有効面積は図 3.17(a) に示す通りであり、今回の測定は RI を SSD の真上に置くようにセットアップしているので、カウントレートの比は

$$TypeA_{p1}: TypeB \perp_{p1}: TypeB \top_{p1} = 1:0.75:0.75$$

(3.3)

となるはずである。しかし実際の測定結果は

$$TypeA_{real}: TypeB \perp_{real}: TypeB \top_{real} = 1:1.27:0.41$$

(3.4)

となっている。TypeB 上下で明らかに有効面積が異なっている。しかも、TypeB 上側のストリップはTypeA よりも有効面積が大きいことになる。この結果より、SSD の有効面積が図 3.17(a) のようではなく、図 3.17(b) のようになっていると仮定してみた。つまり、信号を読み出すために引き延ばされた Al 電極部にも感度があるという仮定である。すると、有効面積の比は

$$TypeA_{p2}: TypeB \perp_{p2}: TypeB \top_{p2} = 1:1.13:0.35$$

(3.5)

となり、上で得られた比率に近い。この仮定を確かめるために、図 3.18 の斜線部 D にコリメートした  $^{133}$ Ba を照射し、TypeB 上側のストリップを読み出した。得られたスペクトルを図 3.19 に示す。このスペクトルには明らかにピークが存在する。よって TypeB は最初に考えられていた図 3.17(a) のような有効面積を持っているのではなく、TypeB 上側のストリップから引き延ばされた Al 電極が電荷を集めており、有効面積は図 3.17(b) のようになっていることがわかった。

図 3.17: (a) TypeA、TypeB の設計から予想される有効面積 (b)TypeA、TypeB で反応したイベント数から仮定した有効面積

次に、TypeB 上側のストリップで得られたスペクトルについて考える。図 3.16 を見るとわかるように、光電ピークは低エネルギー側に tail を引いている。SSD 以外は同じ条件

で測定しているので線源や周囲の物質から放出された X 線ではない。さらに、SSD は同じウェハーで作られているので、TypeA と TypeB の材質は変わらない。よって、この tail は TypeA と TypeB の構造の違いから生じたものであると考えられる。そこで、図 3.18 の斜線部 U にコリメートした  $^{133}Ba$  を照射し、ピークの低エネルギー側に tail が現れるかどうかを調べた。得られた結果を図 3.20 に示す。

#### TypeB

図 3.18: コリメートした X 線の照射領域。U は上側のストリップで  $p^+$  ストリップがある部分。D は上側のストリップで  $p^+$  ストリップ がない部分 (引き延ばされた Al 電極部)

図 3.20 より TypeB 上側のストリップ部だけでは低エネルギー側の tail は存在せず、やはり引き延ばされた Al 電極が原因であると考えられる。さらに、引き延ばされた Al 電極にコリメートした <sup>133</sup>Ba を照射したスペクトル (図 3.19) を見てみると、ピークが約 1650AD-Cchannel にあり、図 3.20 のピークに比べて 4% 程度低いことがわかる。これは、TypeA、TypeB 下側と比較しても同程度低い。このことから、ストリップ部に比べて引き延ばされた Al 電極部は電荷収集効率が悪いということになる。以上のことから、TypeB 上側から得られるスペクトルはストリップ部 (図 3.20) と引き延ばされた Al 電極部 (図 3.19) の足し合わせであると考えられる。図 3.19 と図 3.20 のスペクトルの測定時間は同じなので、両者を足し合わせてみると、図 3.21 のようになり、低エネルギー側の tail を再現している。よって、TypeB 上側ストリップのスペクトルにのみ存在する低エネルギー側の tail は引き延ばされた Al 電極で集められたイベントによるものであると結論付けることができる。

今までの議論で TypeB の上側の引き延ばされた Al 電極部に感度があることがわかったが、このことについて詳しく考える。原因として Al 電極と n バルク部分がコンデンサを形成している (AC 結合) と仮定する (図 3.22)。この場合、 $1~\mu m$  程度の薄さ  $Si_2$  層の上に

電極にコリメートした X 線を照射したと リメートした X 線を照射したときに得ら きに得られたスペクトル

図 3.19: TypeB 上側の引き延ばされた Al 図 3.20: TypeB 上側の p<sup>+</sup> ストリップにコ れたスペクトル

図 3.22: 引き延ばされた Al 電極が n バル 図 3.21: TypeB の引き延ばされた Al 電極 クとコンデンサを形成している場合 部 (図 3.19) とストリップ部 (図 3.20) のス ペクトルの足し合わせ

ある引き延ばされた Al 電極が、真下の n バルク部分を空乏層化し、p+ ストリップがある 電極と同じような電界を作り、電子、ホールを収集する。SiO2層側に電荷(正孔)が集め られると、両隣の $p^+(GND)$ と電位差ができるので電荷は両隣の $p^+$ へ流れる。このとき、 バルクと引き延ばされた Al 電極が作るコンデンサーの電気容量が大きければ、1 イベント 分の電荷量をためることができ、Al 電極に電子を引き寄せるのでシグナルとなって CSA に入力される。ただし、今回の結果から AC 結合によるカップリング損失が 4%程度ある ものと思われる。その後、正孔は両隣の p+へと流れる。逆に電気容量が小さければ、電 荷はほとんどたまることはなく、引き延ばされた Al 電極は X 線に対して感度を持たなく なる。以上のことから、TypeBの構造にした場合、下側のストリップではノイズ特性の 向上が確認されたが、現在の設計では上側のストリップでピークの低エネルギー側に tail が現れることを避けることはできず、X線応答が悪いことがわかった。TypeBの性能を 発揮しようとすると引き延ばされた Al 電極を今よりも細く ( $\sim 5\mu m$ )、 $SiO_2$  層を厚くする 必要がある。今までは引き延ばされた Al 電極の幅が  $30~\mu m$  だったので、 $5\mu m$  に変更す ることにより、キャパシタンスは6分の1になる。そうすれば引き延ばされた Al 電極部 で1イベント分の電荷量をためることができなくなり、低エネルギー側のtailは消えて、 TypeB 上側でも性能の向上が期待できる。

## 3.5 TypeBのリーク電流、Body Capacitanceの考察

次に、Body Capacitance について考察する。X 線の有感領域が図 3.17(b) ならば、図 3.3 のセットアップで測定した TypeB 全体の Body Capacitance は  $p^+$  ストリップが backplane と形成する容量以外に引き延ばされた Al 電極と n バルクが  $SiO_2$  層に作る容量の合成になっているはずである (図 3.23)。しかし、測定値は TypeB を平行板コンデンサと仮定した場合と近い値をとっている。これは直列につながった  $SiO_2$  層をはさむ容量と n バルクをはさむ容量のうち、 $SiO_2$  層はバルクの厚さに比べて十分薄いので、容量は n バルクの

容量に比べて十分に大きく、合成容量はバルク容量で決まるためと考えられる。すると、TypeB の上側、下側のストリップの Body Capacitance はほぼ X 線の有感領域の面積比になるはずである。つまり、図 3.7 で得られた結果を単純に 128 本のストリップで割ることはできず、上側のストリップと下側のストリップで 3:1 の比率で割らなければならない。よって、上側のストリップの 1 本あたりの Body Capacitance はおよそ 2.0 pF、下側のストリップは 1 本あたりおよそ 0.7 pF であると思われる。

図 3.23: TypeB の Body Capacitance の構成

### 3.6 片面シリコンストリップ検出器のまとめ

TypeA、TypeBの基本パラメータとエネルギー分解能を表 3.3 にまとめておく。

| SSD                     | TypeA     | TypeB <b>下側</b>     | TypeB 上側            |

|-------------------------|-----------|---------------------|---------------------|

| リーク電流                   | 130 pA    | 77 pA               | 32 pA               |

| Body Capacitance        | 2.0 pF    | 2.0 pF              | 0.7 pF              |

| Inter-strip Capacitance | 1.9 pF    | 0.8 pF              | 0.8 pF              |

| エネルギー分解能(実測)            | 1.39  keV | $1.24~\mathrm{keV}$ | $1.28~\mathrm{keV}$ |

表 3.3: TypeA と TypeB 上下の基礎パラメータとエネルギー分解能

ストリップを垂直に 2 等分した構造については、TypeB の設計で下側のストリップに関してはノイズ特性の向上が確認できた。しかし、上側のストリップは、引き延ばした Al 電極が太すぎたため、そこでも X 線に対して感度を持ってしまい、結果としてエネルギー分解能が悪くなった。この現象は Al 電極を細くして容量を小さくすれば解決することが期待される。

#### 3.7 両面シリコンストリップ検出器の性能評価

#### 3.7.1 試作した DSSD の基本設計

今回我々のグループは 3 種類の DSSD (P400-64、P800-32、P800-32×2) と 1 枚の片面 SSD (Test structure) を製作した。それぞれの DSSD についての基本設計を表 3.4 にまとめる。P800-32×2 は  $p^+$  ストリップ、 $n^+$  ストリップをともに 2 等分した DSSD で、片面 SSD の TypeB に相当する。P800-32×2 の引き延ばした A1 電極の太さはおよそ  $10~\mu m$  であり、TypeB に比べて細くなっている。

| DSSD            | P400-64             | P800-32             | P800-32×2           |

|-----------------|---------------------|---------------------|---------------------|

| 厚さ              | $300~\mu\mathrm{m}$ | $300~\mu\mathrm{m}$ | $300~\mu\mathrm{m}$ |

| ストリップ数          | 64 本                | 32 本                | 32×2 <b>本</b>       |

| ストリップ間隔         | $400~\mu\mathrm{m}$ | 800 $\mu {\rm m}$   | 800 $\mu {\rm m}$   |

| ストリップの長さ        | $2.56~\mathrm{cm}$  | $2.56~\mathrm{cm}$  | $1.25~\mathrm{cm}$  |

| ストリップギャップ       | $100~\mu\mathrm{m}$ | $100~\mu\mathrm{m}$ | $100~\mu\mathrm{m}$ |

| 引き延ばした Al 電極の太さ |                     |                     | $10~\mu\mathrm{m}$  |

表 3.4: DSSD の基本設計の比較

Test structure は厚さ  $300~\mu m$ 、ストリップ間隔が  $400~\mu m$  の片面 SSD であり、ストリップギャップが異なる 3 つのタイプがひとつのチップ上に乗っている。ストリップギャップとは、ストリップ間隔から電極の幅を引いたもの、つまり  $p^+$  ストリップ間の距離のことで、それぞれ  $100~\mu m$ 、  $130~\mu m$ 、  $160~\mu m$  である。Test structure の設計と写真をそれぞれ図 3.24、図 3.25 に示す。

Teststructure

図 3.25: Teststructure の写真

図 3.24: Teststructure の設計

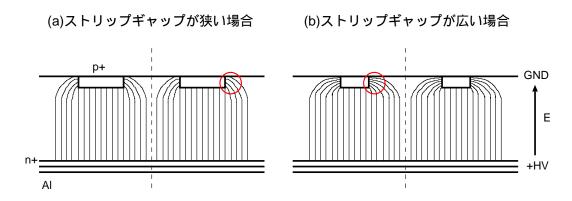

Test structure の製作目的は最適なストリップギャップを探すためである。一般的に SSD はストリップギャップが狭い方が breakdown を起こしにくい。図 3.26 に示すようにストリップギャップが広いと、ストリップの端の部分の電束密度が高くなり、ここから breakdown を起こす。よってストリップギャップは狭い方が高い電圧まで耐えることができる。しかし、ストリップギャップが狭いと Inter-strip Capacitance が大きくなり、エネルギー分解能が悪くなってしまう。そこで、ストリップギャップを広くしつつも、安全性を考慮して実際の動作電圧よりも十分大きい電圧に耐えられるようなストリップギャップにしなければならない。Teststructure ではそれぞれのストリップギャップで breakdown を起こす電圧を調べ、ストリップギャップをどこまで広げられるかを考える。

図 3.26: ストリップギャップと電東密度の相関

#### 3.7.2 I-V curve, C-V curve

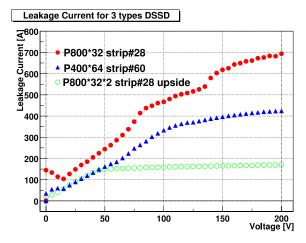

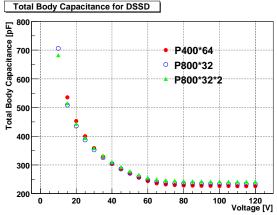

DSSD の基本パラメータであるリーク電流、Body Capacitance、Inter-strip Capacitance を測定した。測定セットアップは基本的に図 3.3 と同じであるが、バイアスをかけるのに Nsub は使わず、 $p^+$  側、 $n^+$  側それぞれで全てのストリップを銅テープにワイヤボンドして、その銅テープに電圧をかけた。測定時の温度は約 20 度である。それぞれの測定結果をそれぞれ図 3.27、図 3.28、図 3.29、図 3.30、に示す。ただし、 $n^+$  ストリップ側はエネルギー分解能を考慮する必要がないので、Inter-strip Capacitance は  $P800\times32$  についてのみ測定した。

リーク電流は  $P800\times32$ 、  $P400\times64$ 、  $P800\times32\times2$  の順で小さくなり、それぞれ 100V で約 470~pA/strip、350~pA/strip、160~pA/strip であった。これらの値は TypeA、 TypeB のリーク電流と比較するとかなり大きい値である。これは DSSD は片面 SSD に比べて両面プロセスを必要とし、クリーンな最新の自動プロセスが使えない。逆面は手動で行うプロセスとなり、必然的にプロセス面を汚してしまうため、表面リーク電流が増加するためである。 DSSD のリーク電流が表面からの寄与が支配的であるとすると、n バルクと  $SiO_2$  層の境界の面積にほぼ比例するので、1 ストリップあたりのリーク電流の比は

$$P800 \times 32_{\text{surface}} : P400 \times 64_{\text{surface}} : P800 \times 32 \times 2_{\text{surface}} = 1 : 1 : 0.5$$

(3.6)

図 3.27: 3 種類の DSSD のリーク電流の 比較

図 3.28: 3種類の DSSD の Total Body Capacitance の比較

**3**.29: Capacitance(p<sup>+</sup> ストリップ) の比較

3 種類の DSSD の Inter-strip 図 3.30: DSSD P800×32のn<sup>+</sup> ストリップ **O** Inter-strip Capacitance

となる。 $P800 \times 32 \times 2$  はストリップを垂直に 2 等分したために、n バルクと  $SiO_2$  層の接触 部分が増えているが、その影響は全体の約1%しかない。しかし、測定結果は

$$P800 \times 32_{measured} : P400 \times 64_{measured} : P800 \times 32 \times 2_{measured} = 1.3 : 1 : 0.46$$

(3.7)

であり、あまり一致していない。そこで、バルクからのリーク電流の寄与も無視できない と考えると、バルクのリーク電流は体積に比例するので

$$P800 \times 32_{\text{bulk}} : P400 \times 64_{\text{bulk}} : P800 \times 32 \times 2_{\text{bulk}} = 2 : 1 : 1$$

(3.8)

となる。よって、表面からのリーク電流とバルクからのリーク電流の寄与が4:1の割合

であれば、実測値に近い比率となる。

Total Body Capacitance は逆バイアスをかけていくと徐々に小さくなっていき、P800×32、P400×64、P800×32×2でそれぞれ 230 pF、230 pF、240 pF となった。DSSD を平行板コンデンサと仮定すると、その容量は 230 pF となり、実測値とほぼ一致している。よって 3 種類の DSSD の 1 ストリップあたりの Body Capacitance はそれぞれ 3.6 pF/strip、7.2 pF/strip、3.6 pF/strip となる。2 等分 DSSD である P800-32×2 は引き延ばした Al 電極が 細いので、単に Total Body Capacitance を 64 ストリップで割った値である。P800×32、P400×64 は約 65V で一定の値を取り、全空乏層化されているのがわかる。これに対し、P800×32×2 は約 110V で全空乏層化が起こっている。これは測定した複数のストリップで同じ現象が見られた。TypeA、TypeB の全空乏層化電圧はほとんど変わらなかったので、構造による違いとは考えにくい。 $\S 2.3.3$  で述べたように、全空乏層化電圧は SSD の厚さと比抵抗で決まり、厚さは同じなので P800×32×2 の比抵抗は P800×32、P400×64 に比べると半分くらいしかないと思われる。

$p^+$  側の Inter-strip Capacitance も Body Capacitance と同様、逆バイアスをかけていくと小さくなってやがて一定値を取っている。 $P800\times32$ 、 $P400\times64$ 、 $P800\times32\times2$  でそれぞれ 2.7~pF/strip、2.7~pF/strip、1.3~pF/strip となった。Inter-strip Capacitance は主に  $p^+$  ストリップ間の距離とストリップの長さに比例するので、

$$P800 \times 32_{\text{Inter-strip}} : P400 \times 64_{\text{Inter-strip}} : P800 \times 32 \times 2_{\text{Inter-strip}} = 2 : 2 : 1$$

(3.9)

という関係になることが予想でき、結果はこの関係とよく一致している。 $n^+$  ストリップの Inter-strip Capacitance は、図 3.30 より  $0 \sim -10$  V の領域で負の容量が測定されている。 $p^+$  ストリップの場合、電圧をかけていなくてもn バルクと空乏層を形成するため、0 V でもコンデンサの働きを持つが、 $n^+$  ストリップはn バルクと空乏層を形成しないので、0 V 付近ではコンデンサのように振舞わない。その結果、キャパシタンスメーターで負の値になったと考えられる。さらに逆バイアスをかけていく正の値をとり、およそ 65 V くらいで一定値に落ち着いている。これより、 $n^+$  ストリップの Inter-strip Capacitance は約 4.6 pF/strip であることがわかった。

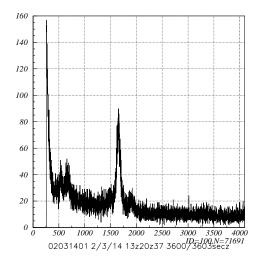

#### 3.7.3 Test structure を用いた p<sup>+</sup> ストリップ間距離の最適化

$\S 3.7.1$  で述べたように、Test structure には 3 種類のストリップギャップ  $(100~\mu\mathrm{m},~130~\mu\mathrm{m},~160~\mu\mathrm{m})$  を持った構造があり、これを利用して breakdown を起こさず、安全に全空 乏層化電圧をかけることができるストリップギャップを見付けることができる。pn 接合 ダイオードが breakdown を起こすとリーク電流が急激に上昇する。よって、I-V curve を 測定することで breakdown を起こす電圧を調べる。

測定セットアップは基本的に図 3.3 と同様、Nsub に正の電圧をかけていき、読み出すストリップ以外のストリップは GND に落とした。測定時の温度は約 20C である。測定結果を図 3.7.3 に示す。最も早く breakdown を起こすことが予想されるのはストリップギャップが  $160~\mu \mathrm{m}$  の構造であるが、 $200~\mathrm{V}$  まで電圧をかけても breakdown は確認できなかった。

全空乏層化電圧、すなわち動作電圧は  $70~V\sim 100~V$  であることが予想されるので、その 2 倍にあたる 200~V の電圧で breakdown を起こさないのであれば、十分安全であると言える。以上のことから、ストリップギャップが  $160~\mu m$  でも問題なく動作可能であることがわかった。

図 3.31: Test structure のリーク電流の電 圧依存性

それぞれのストリップギャップのリーク電流の大きさを比較してみるとおよそ

$$gap100\mu m : gap130\mu m : gap160\mu m = 1 : 1.2 : 1.4$$

(3.10)

となっている。表面リーク電流が支配的だとすると、n バルクと  $SiO_2$  の境界に生じた欠陥によるので、リーク電流の大きさはストリップギャップに比例し、

$$gap100\mu m : gap130\mu m : gap160\mu m = 1 : 1.3 : 1.6$$

(3.11)

となるはずである。今回はこれに近い値であり、表面リーク電流からの寄与が大きいことがわかる。

#### 3.7.4 両面シリコンストリップ検出器のエネルギー分解能測定

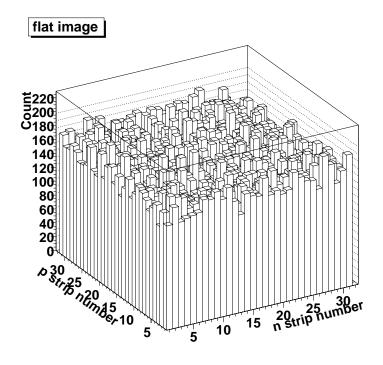

DSSD(P400×64) に X 線を照射し、単体 CSA を用いて 1 本の  $p^+$  ストリップの X 線応答を調べた。1 本の  $p^+$  ストリップを基板にワイヤボンドして CSA に接続し、残りの  $p^+$  ストリップは全て GND に落とした。CSA は片面 SSD のときと同じ Clear Pulse 社製の Model 580K を用い、shaping Amplifier は ORTEC 社製 Model 571 を使った。電圧は  $n^+$  ストリップに 80 V の逆バイアスをかけて全空乏層化させ、shaping time は 2  $\mu$ sec でデータを取得した。測定時の温度は約 20C である。使用した X 線源は 241 Am  $(13.9 \text{ keV} \times 17.6 \text{ keV} \times 21.0 \text{ keV} \times 26.3 \text{ keV} \times 59.5 \text{ keV})$  であり、得られたエネルギー分解能は 59.5 keV のピークに対して 1.35 keV となった  $(\boxtimes 3.7.4)$ 。

$\S 3.7.2$  より、DSSD P400×64 の Body Capacitance は 3.6 pF、Inter-strip Capacitance は 2.7 pF である。これより、DSSD P400×64 で予想されるエネルギー分解能を計算して みる。使用した CSA は変わらないので、式 3.2 より  $ENC_{amp}=110~(e^-)$ 、リーク電流は 80 V で 330 pA なので、 $ENC_{lc}=89~(e^-)$ 、59.5 keV の X 線で生成される電子ホール対の 統計揺らぎは  $ENC_{stat}=40~(e^-)$  となる。よって、 $ENC_{total}=150~(e^-)$  となり、これを eV の単位に直すと  $\Delta E=1.3$  keV になる。よって、予想されるエネルギー分解能と実際に得られたエネルギー分解能は一致しているので、DSSD 読み出しのノイズ成分をよく理解できていることがわかった。

図 3.32: DSSD P400×64 で得られた <sup>241</sup>Am のエネルギースペクトル

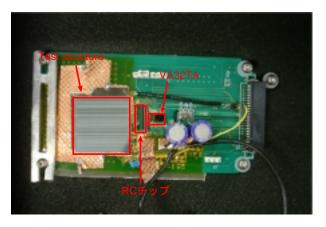

#### 3.8 RCチップ

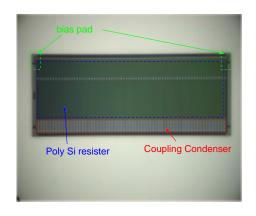

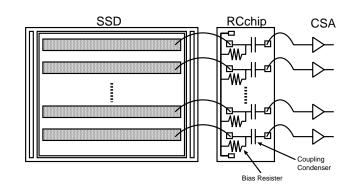

RC チップは GLAST 衛星のトラッカーに用いられているような今までの SSD からカップリングコンデンサとバイアス抵抗を抜き出し、別のシリコンチップ上に製作したものである (図 3.1)。 RC チップの写真を図 3.33 に示す。 RC チップの製作目的は

- 大きなバイアス抵抗を容易に作ることが可能であり、エネルギー分解能の向上につ ながる。

- カップリングコンデンサは 97 %以上の歩留まりを達成することは難しく、これを別のチップに作ることによって、SSD(特に DSSD) の歩留まりをあげる。

- より良いノイズ特性を得るためにSSDをCSAにDC結合できる方式も選択できる。

などが挙げられる。RC チップの使用方法は図 3.34 のように SSD と読み出し系の間に入れ、バイアス電圧の供給やリーク電流のカットなどを行う。TypeA とは異なり、バイアスリングと全ての  $p^+$  ストリップがバイアス抵抗を介して接続されているので、バイアスリングを用いて簡単に SSD、RC チップにバイアスをかけることができる。製作した RC

図 3.33: RC チップ  $(200 \ \mu m \$ ピッチ) の写真 図 3.34: SSD、RC チップ、CSA の接続方法

チップはストリップピッチの異なる 3 種類  $(200~\mu\mathrm{m},~400~\mu\mathrm{m},~800~\mu\mathrm{m})$  がある。バイアス 抵抗はそれぞれ  $1.0~\mathrm{G}\Omega$ 、 $2.5~\mathrm{G}\Omega$ 、 $6.0~\mathrm{G}\Omega$  と非常に大きな値であり、GLAST 衛星の SSD のバイアス抵抗がおよそ  $50~\mathrm{M}\Omega$  であることと比べるとジョンソンノイズが小さくなることが期待できる。また、カップリングコンデンサはそれぞれ約  $22~\mathrm{pF}$ 、約  $52~\mathrm{pF}$ 、約  $110~\mathrm{pF}$  である。

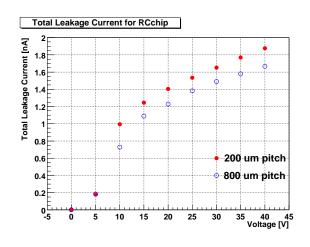

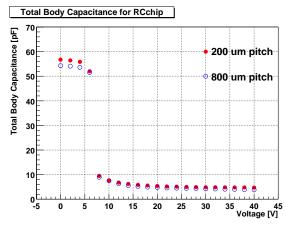

図 3.1 に示すように、RC チップは SSD と似た構造を持っている。よって、RC チップ はリーク電流、Body Capacitance、Inter-strip Capacitance を持ち、エネルギー分解能に 影響を与える。そこで、RCチップの特性を知るために、これらの値を測定した。測定時 の温度は約20度であり、測定に使った電源、電流系などはTypeAのときと同じである。 Inter-strip Capacitance の測定セットアップは基本的に図 3.3(c) と同じであるが、リーク 電流、Body Capacitance は1ストリップあたりの値が小さいので、バイアスリングを用 いてチップ全体のリーク電流、全体のBody Capacitance を測定した。測定結果を図3.35、 図 3.36、図 3.37 に示す。リーク電流は全体でおよそ 1.8 nA であり、200  $\mu$ m ピッチの RC チップでは 1 ストリップあたり約 30 pA、800  $\mu m$  ピッチでは約 110 pA である。BodyCapacitance は全体で約 4.5 pF であり、200  $\mu$ m ピッチの RC チップでは 1 ストリップあ たり約 0.07 pF、800 μm ピッチでは約 0.28 pF である。Inter-strip Capacitance は 200 μm ピッチ、 $400 \mu m$  ピッチ、 $800 \mu m$  ピッチの順で大きくなっている。Inter-strip Capacitance は主にストリップの長さとp+ストリップの幅に依存する。TypeA、TypeB、DSSDのよう にストリップの長さがp+ストリップの幅よりも十分大きい場合、Inter-strip Capacitance は主にストリップの長さに依存するが、RC チップのようにストリップが短く、 $p^+$  スト リップの幅とあまり変わらない場合は p<sup>+</sup> ストリップの幅も Inter-strip Capacitance に大 きな影響を与える。今回の測定結果はこの p+ ストリップの幅を反映していると思われる。 また、Inter-strip Capacitance は TypeA や DSSD のように電圧を上げることによって減 少せず、常に一定の値を取っている。これは RC チップのストリップ間隔が狭いので (~数  $\mu$ m)、電圧をかけていない状態ですでに隣の  $p^+$  ストリップが形成する空乏層とくっついているためだと考えられる。

図 3.35: RC チップ全体のリーク電流

図 3.36: RC チップ全体の Body Capacitance

図 3.37: RC チップの 1 ストリップあたり の Inter-strip Capacitancek

図 3.38: RC チップを用いた TypeA で測 定した <sup>133</sup>Ba のエネルギースペクトル

実際に図 3.34 のように TypeA と CSA の間に RC チップを入れて、TypeA に  $^{133}$ Ba を 照射した。TypeA には今まで同様 100 V の逆バイアスをかけ、RC チップには空乏層化するために 20 V 逆バイアスをかけた。測定温度は約 20 度で、shaping time = 2  $\mu sec$  とし

た。得られたスペクトルを図 3.38 に示す。30.9 keV のエネルギー分解能は 2.0 keV であり、RC チップがノイズ特性に大きく影響を及ぼしていることがわかる。TypeA のみで実際に得られたエネルギー分解能と、RC チップのリーク電流、Body Capacitance、Inter-strip Capacitance から計算されるエネルギー分解能は 1.5 keV である。さらに、200  $\mu m$  間隔のRC チップのカップリングコンデンサは約 22 pF と小さく、カップリング損失が 14 %程度あることが確認されている (岡田、2002)。そのために 1.5 keV のエネルギー分解能にたいして実際には約 1.8 keV と悪化する。この値は実測データから求めたエネルギー分解能 (2.0 keV) と近い値である。

# 第4章 多チャンネル同時計測に向けた読 み出しシステム立ち上げ

DSSD の全てのストリップを読み出すときに、単体の CSA、Shaping Amplifier、トリガーロジックを用いていると読み出しシステムが物理的に巨大になり、あまり現実的とは言えない。さらに多重コンプトンガンマ線カメラを考えたときには読み出すチャンネル数は劇的に増大するので、今までのシステムでは完全に破綻する。そこで、低ノイズであるとともに、非常にコンパクトな新しい読み出しシステムの構築が必要である。この章では我々が扱った多チャンネル読み出しシステムの概要を説明し、その立ち上げ作業について後半で述べる。

#### 4.1 VA32TA

#### 4.1.1 VA32TA とその特徴

近年、高エネルギー物理学実験の領域で、荷電粒子からの小さな信号を測るためにシリコンストリップ検出器の読み出し系として複数の CSA、Shaping Amplifier を搭載した低ノイズアナログ LSI(Viking-architecture chip:VA) とトリガー用アナログ LSI(Triggering-architecture chip:TA) が IDEAS 社によって開発されてきた。アナログ LSI の低ノイズ化が進んだことにより、SSD と X 線の反応によって生じる少ない電荷量も精度良く測定することができるようになってきた。

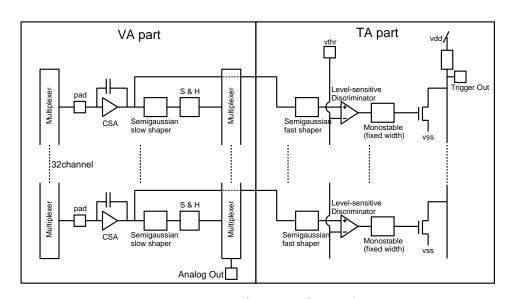

我々のグループは VA32C、TA32C を基に IDEAS 社と協力して VA32TA チップを開発した (図 4.1)。VA32TA は  $0.35~\mu m$  の CMOS 技術を用いて製造された  $32~\pi v$  ンネルの読み出し系を持つ多チャンネル同時計測用アナログ LSI である。ひとつのチャンネルは、CSAとそれに続く slow shaping amplifier、サンプルホールド回路、マルチプレキサからなる VA 部と、fast shaping amplifier、ディスクリミネータからなる TA 部にわけられる。VA部が ADC に入力するための波形生成を担当し、TA 部はトリガー信号を作り出す役割を持つ。ひとつのチャンネルのブロックダイアグラムを図 4.2 に示す。また、VA32TA の仕様を表 4.1 にまとめる。

VA32TA が持つ特徴を以下に挙げ、それぞれ説明していく。

#### 1. 低ノイズ

VA32TA は極めて低ノイズな設計であり、アンプノイズは

$$ENC_{amp}$$

(e<sup>-</sup>) =  $(45 + 19 \times C(pF))/\sqrt{\tau}$  (µsec) (4.1)

図 4.1: VA32TA チップの写真

表 4.1: VA32TA の基本仕様

| サイズ         | $7.035 \times 3.385 \times 0.725 \text{ mm}$ |

|-------------|----------------------------------------------|

| チャンネル数      | 32                                           |

| パッド間隔       | $100~\mu\mathrm{m}$                          |

| 消費電力        | $6.3 \mathrm{\ mW/channel}$                  |

| Max Readout | 10 MHz                                       |

図 4.2: VA32TA のブロックダイアグラム

で表すことができる。C は CSA にロードされる容量である。

#### 2. 電流補償機能

SSD の読み出しで最も良いノイズ特性を達成するためには、SSD と VA32TA を DC 結合しなければならない。その場合、SSD のリーク電流が CSA のフィードバック抵抗に流れ込み、正常な動作ができなくなることが大きな問題になってくる。この問題を解決するために、リーク電流と同じ大きさで逆向きの電流を CSA のフィードバック抵抗に流すことによってその影響を打ち消し、リーク電流の流れ込みが大きな環境でも VA32TA チップを動作可能にする機能を電流補償機能という。また、この機能を用いれば AC 結合したときのカップリングコンデンサがショートしたとしてもそのチャンネルで読み出し続けることが可能である。

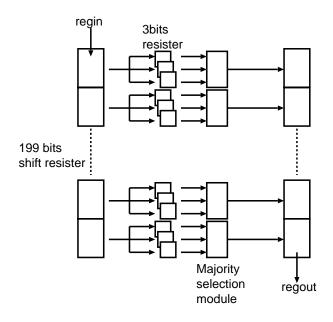

#### 3. Majority selection module for Single-Event Upset(SEU)

宇宙空間には重い荷電粒子がバックグラウンドとして多く存在する。重い荷電粒子はFETの内部で局所的に強い電離作用をもたらし、その結果レジスタのビットを反転させてしまうことがある。もしセットアップ信号のビットが変わってしまうと VA32TA チップが誤動作してしまう。そこで、図 4.3 のようにレジスタの値を 1 ビットずつ 3 つのレジスタに入れ、Majority selection モジュールに送る。Majority selection モジュールは 3 つのレジスタに保存された値を比較し、多い方の値を返す。これによってビット反転が起こったとしてもその影響を取り除くことができる。

図 4.3: Majority selection module の概要

#### 4. mbias

電源系のバイアスを除き、VA32TA に与えなければならないバイアス電流は mbias のみである。その他全ての bias に流すバイアス電流は mbias を抵抗分割してつくり 出される。それぞれの bias は  $3 \sim 5$  ビットの調整機能を持っており、抵抗分割の程度を決めることができる。この bias に与える電流を VA32TA 内部で調整するための

3~5 ビットを internal DACs(Digital to Analog Convertor) という。また、internal DACs の調整では足りない場合、VA32TA にはこれらの bias を外部から個々に供給することも可能な設計になっている。

#### 5. 199 ビットシフトレジスタ

が可能である。

VA32TA チップは 199 ビットのシフトレジスタを持っており、regin 信号と clkin 信号によって 199 ビットがロードされる。199 ビットの内訳は次の通りである。

- (a) internal DACs (35 ビット) 今までのVAチップではさまざまな bias を外部に取り付けた可変抵抗などで制 御してきたのに対し、DAC を用いることにより効率良く最適化、および制御

- (b) スレッショルド調整用 DAC (4 ビット×32 チャンネル) vthr で全てのチャンネルを同じスレッショルドに設定しても、各チャンネルの ゲインの違いなどにより、入力電荷量に対して一定のスレッショルドをとらない。そこで、各チャンネルのスレッショルドを微調整するためにひとつのチャンネルにつき 4 ビットの DAC が設けられている。

- (c) Enable or Disable (32 ビット) 各チャンネルに対して、イベントが起きたときにトリガーを立てる (Enable) か 立てない (Disable) かを選択するための DAC。

- (d) Test\_on (1 ビット) テストモードをオンにするかオフにするかを切替えるための DAC。

- (e) CC\_on (1 ビット) 電流補償機能をオンにするかオフにするかを切替えるための DAC。

- (f) Nside (1 ビット)入力電荷量が正か負かを選択するための DAC。

- (g) Tp300 (1ビット) fast shaper の peaking time を選択するための DAC。"1" の場合 peaking time は 300 nsec、"0" の場合は 75 nsec である。

#### 6. テストモード

$\operatorname{cal}$  ピンに外部から電荷パルスを入力すると、指定したチャンネルの  $\operatorname{CSA}$  に入力することができる。このモードを用いることで  $\operatorname{VA}$  部、 $\operatorname{TA}$  部が正常に動いているかチェックすることができる。

#### 4.1.2 VA32TA の動作に必要な制御信号

VA32TA を動かすための主な入出力信号を以下にまとめる。

電源系

- dvdd デジタル系の電源。+1.5 V

- dvss デジタル系の電源。-2.0 V

- avdd アナログ系の電源。+1.5 V

- avssアナログ系の電源。-2.0 V

- GND グラウンド

#### デジタル I/○

- Holdb (IN) サンプルホールド回路をスタートさせる入力信号。

- shift\_in\_b (IN) マルチプレキサで読み出しをスタートさせるための入力信号

- shift\_out\_b (OUT) マルチプレキサでの読み出しを終了をつげる出力信号

- Ckb (IN) マルチプレキサでの読み出しのときのクロック信号。読み出 すチャンネルを変更するのに使われる。入力信号。

- regin (IN) VA32TA のセットアップのための入力信号 (199 ビットシフトレジスタ)

- regout (OUT) 199 ビットシフトレジスタからの出力信号。今までレジス タに入力されていた信号を出力するので、そのチェックを行うことができる。

- clkin (IN)

199 ビットシフトレジスタに regin を書き込むときのクロック信号。入力信号。

- ta、tb (OUT) トリガー出力信号。差動信号である。

- Dreset (IN)デジタル系のリセット信号。入力信号。

#### • アナログ I/O

- mbias (IN)全ての bias を作り出すメインとなる bias。初期値は 500μA/chip

- outp、outm (OUT) VA32TA の正出力と負出力。差動出力 (signal = outp outm)。

- vfp (IN)CSA のフィードバック抵抗にかかるバイアス電圧。(internal DACs)

- ibuf (IN)差動出力の直前にあるバッファのバイアス電流。(internal DACs)

- vfsf (IN) fast shaping amplifier のフィードバック抵抗にかかるバイアス電圧。(internal DACs)

- vfs (IN) slow shpaing amplifier のフィードバック抵抗にかかるバイアス電圧。(internal DACs)

— sha\_bias (IN) slow shaping amplifier のバイアス電流。(internal DACs)

— pre\_bias (IN) CSA のバイアス電流。(internal DACs)

- vthr (IN) ディスクリミネータのスレッショルド電圧。(internal DACs)

trgWbias (IN)トリガー出力のパルス幅を決めるバイアス電流。(internal DACs)

- cal (IN)テストパルスの入力信号。

#### 4.1.3 VA32TA の動作原理

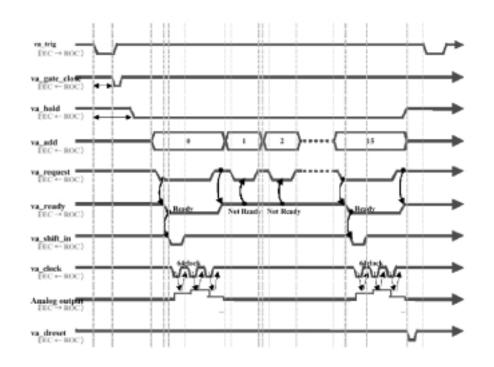

SSD から VA32TA のあるチャンネルに電荷が入力されると、まず CSA を通り slow shaping amplifier (VA 部) と fast shaping amplifier (TA 部) にわかれる。fast shaping amplifier 出力がディスクリミネータで指定したスレッショルド (vthr) を超えると、そのディスクリミネータ出力は他のチャンネルのディスクリミネータ出力と or ゲートでつながれており、ta というトリガー出力に変換される。ta が生成されると図 4.4 のようにある遅延をおいて全てのチャンネルのサンプルホールド回路のスタートタイミングを表す Holdb 信号を送り、各チャンネルの波高値をホールドする。次に shift\_in\_b を送り、shift\_in\_b がオンになっているときに Clkb を 1 クロック入れる。するとマルチプレキサが最初のチャンネルとつながり、ホールドされていたデータを読み出す。あとは次々と Clkb 信号を送るとそれに同期して 1 チャンネルずつ読み出しが行われる。最後に shift\_out\_b を送ることで読み出しが終わる。

図 4.4: VA32TA の読み出しタイミングチャート

テストモードで動作させる場合もチャンネルの選択は読み出しのときと全く同じであ

り、 $shift_in_b$  と Clkb で選択する。cal に電荷パルスを入力すると、CSA の前にあるマルチプレキサ (図 4.2) で選択されたチャンネルに電荷が送られ、そのチャンネルの動作を確認することができる。

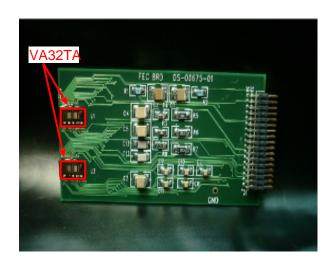

#### 4.2 フロントエンドカード

VA32TA がマウントされている基板をフロントエンドカード (FEC) という。FEC には 2 枚の VA32TA チップがマウントされており、1 枚の FEC で 64 チャンネルの読み出しが 可能である。FEC の写真を図 4.5 に示す。FEC のサイズは  $30~\mathrm{mm} \times 60~\mathrm{mm}$  であり、2 枚の

図 4.5: フロントエンドカードの写真

チップ間距離は 12.5 mm である。後段の読み出しシステムとの接続には 34 ピンのフラットケーブルを用いている。また、VA32TA チップの横に SSD と RC チップにバイアスを供給するためのボンディングパッドを設けている。

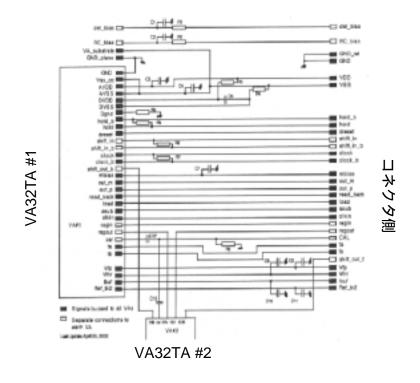

図 4.5 を見るとわかるように、FEC 上にはたくさんの抵抗とコンデンサが実装されている。これらはローパスフィルターやデカップルコンデンサ、デジタル信号のターミネーションなどに使われている passive なものである。図 4.6 には FEC の回路設計を示す。図が繁雑になるのを避けるために図 4.6 中に明記していないが、コネクタ側と VA32TA#1 のみがつながれている全ての配線は VA32TA#2 とも配線を共有している。配線を共有していないのは regin、regout、shift\_in\_b、shift\_out\_b、cal である。2 枚の VA32TA を同時に制御し、64 チャンネルの読み出し系として動作させるためには、コネクタ側から送られてきた regin、shift\_in\_b をまず VA32TA#1 に入力し、#1 の regout、shift\_out\_b を#2 の regin、shift\_in\_b として入力しなければならない。cal は $\$51\Omega$  でターミネートされてから二手にわかれ、\$1.8 pF のコンデンサを介して VA32TA の cal パッドに接続されている。これによりコネクタ側の cal からテストパルスが入力されると、テストパルスの電圧値を電荷量に変換し、VA32TA の cal パッドを通って CSA に入力することができる。

図 4.6: FEC の回路設計

FEC はノイズ特性を向上させるためにデカップルコンデンサに  $22~\mu F$  というおおきな 容量を持たせている。また、差動入出力は互いに並べて配線し、EMI(Electro Magnetic interference) の影響を小さくしている。

#### 4.3 VA-DAQ

VA-DAQ は VA/TA チップの制御、読み出しを目的とした IDEAS 社製のデータ取得システムである。さまざまな研究機関ですでに使用されており、VA/TA チップの読み出しが行われている。VA-DAQ の写真を図 4.7 に示す。大きさは約 25 cm×25 cm、高さ 10 cm のケースに 2 枚の基板が入っている。VA-DAQ は主に 5 つのパートに分けられ、それぞれ PARIO、BIAS、SUPPLY、ADC、PULSE と呼ぶ。PARIO は PC と VA-DAQ をつなぐパラレルポートのインタフェースであり、BIAS は VA チップに必要なバイアスをつくり出すと同時にその電圧値と電流値のモニタリングを行う。SUPPLY は VA チップを動作させるのに必要な電源を作る。VA-DAQ の VA-DAQ の V

VA-DAQ はPC とパラレルポートで接続し、LabView を用いて完全に制御できる。Lab-

図 4.7: VA-DAQ の写真

View は National Instruments 社が開発した graphical programable language で、視覚的な操作でプログラムを組むことができる。LabView プログラムを用いて VA/TA チップの基礎評価や読み出しを行うことができる。以下に LabView で設定できる主なものを挙げる。

- VA32TA に与えるバイアスを決定する。

- 199 ビットシフトレジスタの値を決め、デジタル信号を VA32TA に送る。

- Hold 信号のタイミングを 1 イベントごとに少しずつずらして、slow shaping amplifier 出力をサンプリングすることにより、slow shaping amplifier 出力の波形を確認できる。

- VA-DAQ 内でテストパルスを発生させ、VA32TA の cal に入力することで各チャンネルのゲインを測定できる。

- 全チャンネルのペデスタル (ゼロ点からのずれ) とノイズの大きさを測る。

- ノイズの大きさとゲインから各チャンネルの ENC を求める。

- 各チャンネルのスレッショルドのずれを測定、補正できる。

- SSD などの検出器を VA32TA に接続した場合、多チャンネル読み出しの制御し、リアルタイムでデータをヒストグラムにする。

VA-DAQ は 50 ピンの half-pitch コネクタが採用されている。我々のグループが製作した FEC は 34 ピンの half-pitch コネクタであるため、VA-DAQ と FEC を接続するためには VA-DAQ のコネクタから不必要なものをはぶき、34 ピンに変換することが必要である。

#### 4.4 新しい読み出しシステム

#### 4.4.1 システムの概要

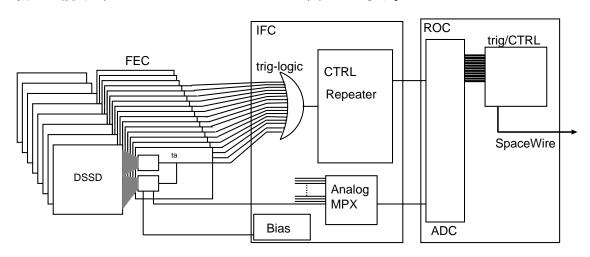

多重コンプトンガンマ線カメラを考えた場合、VA-DAQ を用いた読み出し系ではいくつかの問題点がある。まず、衛星搭載に必要な省消費電力、省スペース、放射線耐性にマッチしていない。次に、多重コンプトンガンマ線カメラは SSD やピクセル検出器の組み合わせなので、読み出すチャンネルは相当な数になり、たくさんの FEC を扱わなければならない。VA-DAQ で複数の FEC を制御する場合はセットアップのための信号やデータを読み出すときの信号を直列につなげなければならないので、複数の FEC のうちどこかひとつの配線が切れてしまった場合、直列につながっている全ての FEC に信号を送れなくなってしまうため、安全性に欠ける。最後に、イベントがヒットした場合、直列につながっているので全てのチャンネルを読み出さなければならなず、高速読み出しが行えない。硬 X 線ガンマ線領域ではバックグラウンドが多いので、高速読み出しは必要不可欠である。

そこで、我々のグループは大阪大学とクリアパルス社を中心に多数の VA32TA チップの制御、読み出しを行える新しい読み出しシステムを開発した。この読み出しシステムは FEC(VA32TA)、バイアスボード、インタフェースカード (InterFace Card:IFC)、ROC(Read Out Controller) モジュール、SpaceWire VME モジュールから成り、非常にコンパクトな設計にもかかわらず、16 枚の FEC(1024 チャンネル) を並列に接続できる。新しい読み出しシステムのダイアグラムを図 4.8 に示す。

図 4.8: 新しい読み出しシステムのダイアグラム

#### バイアスボード

IFC に与える電源から VA32TA チップに必要な電源 (AVSS、AVDD) を作り、供給するためのボード。また、mbias、vfp に与えるバイアス電圧、バイアス電流を可変抵抗を用いて作り出すためのボード (図 4.9)。vthr、Ref\_bi の値を VA32TA の internal DACs で調整で

きる範囲以上に設定する場合は、同じく可変抵抗で調整し、供給することができる。バイ アスボードはこれら以外の信号に対して何の影響も与えない。

図 4.9: バイアスボードの写真

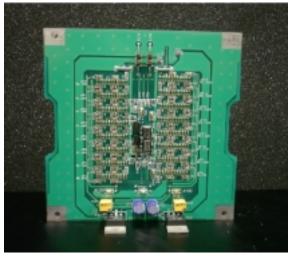

#### インタフェースカード (IFC)

IFC は FEC と ROC モジュール間のインターフェースとなるモジュールであり、クリアパルス社によって開発された (図 4.10)。 FEC を 16 枚 (1024 チャンネル) 接続できるにもかかわらず、 $10~\mathrm{cm}\times10~\mathrm{cm}$  の基板の 2 層構造になっており、極めてコンパクトな設計になっている。IFC には 16 個の 34 ピン half-pitch コネクタが並んでおり、フラットリボンケーブルで FEC と接続される。

IFC の役割は主に 3 つあり、ひとつは FEC-ROC 間でやりとりするデジタル信号 (regin、holdb など) のロジックレベルを+1.5 V、-2 V(VA32TA) から+3 V、GND(ROC) に変換することである。二つ目は 16 枚の FEC からのトリガー信号 (ta) を IFC に搭載されている CPLD で OR をとり、ひとつのトリガー信号として ROC に送ることである。最後は VA32TA 出力 (outp - outm) に対してオフセット調整、ゲイン調整である。

m VA32TA 出力の差動電流は IFC に入ると  $m 1~k\Omega$  でターミネートされ、電圧値に変換される。その後、オフセット調整回路、ゲイン調整回路を通って差動電圧として ROC に送られる。

#### ROCモジュール

ROC は新しい読み出しシステムを制御するモジュールであり、大阪大学の能町グループによって開発された (図 4.11)。IFC と同じく  $10~\mathrm{cm} \times 10~\mathrm{cm}$  の基板上に CPLD、フラッシュ ADC、SDRAM、 $48~\mathrm{MHz}$  クロックジェネレータを搭載している。CPLD はプログラム可能な複合論理デバイスである。CPLD を用いることにより、複雑な論理回路を何度も書き換え可能となり、汎用性の高い極めてコンパクトな制御モジュールとなっている。ROC

図 4.10: IFC の写真。左図が ROC と接続する基板。右図は 16 個の 34 ピン half-pitch コネクタが並んでおり、FEC と接続する基板

図 4.11: ROC の写真

は+3 V、GND の電源供給で動作し、デジタル信号のレベルは Low LevelTTL(LLTTL: +3 V、GND) である。IFC との接続は 34 ピンの half-pitch フラットケーブルを用いている。 ROC には主に 2 つのシーケンスがあり、ひとつはセットアップシーケンス、もうひとつが読み出しシーケンスである。セットアップシーケンスはセットアップする FEC のアドレスを選択した後、199 ビットシフトレジスタの値を設定し、Clkin 信号と同期させて VA32TA チップの regin 信号として送るモードである。このセットアップは 16 枚の FEC に対して並列に処理されるため、16 枚の FEC のセットアップを順に行うことが可能なだけでなく、FEC1 枚だけのセットアップ信号を書き換えることができる。FEC のアドレス、レジスタの値は SpaceWire VME モジュールを介して PC 上で設定できる。読み出しシー

ケンスは多チャンネル読み出しの制御とデータ取得を担当している。タイミングチャートは基本的に VA-DAQ と同じであるが、大きな特徴として 16 枚の FEC 全てを読み出さず、ヒットした FEC のデータのみを読み出す。それによって読み出しにかかる時間を短縮できるのである。これは読み出すチャンネル数が増えれば増えるほどその重要性は増していく。実際に ROC を用いて 16 枚の FEC からのデータを読み出す場合のタイミングチャートを図 4.12 に示す。IFC から ROC にトリガー信号が入力されると ROC が hold 信号を

図 4.12: 16 枚の FEC からのデータを読み出すときのタイミングチャート

出して全てのチャンネルのデータをホールドする。その後、 $va_add$  信号を IFC に送って FEC を指定し、IFC からの  $va_request$  信号を用いてその FEC でヒットしたかどうかを確認する。ヒットしていた場合、IFC から ROC に  $va_ready$  信号が送られ、64 チャンネルの データを読み出す。読み出しが終われば  $va_add$  で次の FEC に移り、同様に FEC からの  $va_ready$  信号を確認するが、もし  $va_ready$  信号が返されなければその FEC のデータは読み出さず、 $va_add$  信号で次の FEC へ移動する。トリガー信号が一回入ると、16 枚の FEC に対してこれらの動作を行い、終了した時点で ROC からデジタル系のリセット信号である  $va_reset$  を IFC に送り、次のイベントに備える。現段階では 1 イベントのデータ取得にかかる時間は FEC1 枚あたりおよそ 6 msec である。

#### SpaceWire VME モジュール

ROC と PC のインタフェースには SpaceWire VME モジュールを用いる。データ転送速度は  $2 \sim 100 \text{ Mbps}$  と極めて高速通信が可能である。現在は 24 Mbps で動作を行ってい

る。 $\mathrm{ROC}$  とは  $100~\Omega$  のツイストペアケーブルで接続している。

# 第5章 VA32TAを用いたシリコンスト リップ検出器の多チャンネル同時 計測

今までは1 ストリップからのX 線応答を単体のCSA で読み出し、SSD の性能を評価してきたが、実際には多チャンネルの同時計測をしなければならない。そこで、4 章で述べた VA32TA と VA-DAQ を用いた読み出しシステムを用いて3 章で述べた片面 SSD(Test structure) の多チャンネル同時計測を試みた。

#### 5.1 実験セットアップ

VA32TA チップを用いた多チャンネル同時計測システムとして、次の二つのモジュールを製作した。

- 1)VA32TA RC チップ Test structure (AC 結合モジュール)

- 2)VA32TA Test structure (DC **結合モジュール**)

VA32TA から VA-DAQ までのバイパスに 4.2 で述べた FEC は使わず、より構造の簡単な VA32TA 評価ボードを用いた。この評価ボードには 1 つの VA32TA チップがマウントされている。それ以外には、cal のコンデンサ  $(1.8~\mathrm{pF})$  と、AVDD と AVSS が  $10~\mu\mathrm{F}$  のコンデンサで GND にカップルされ、DVDD と DVSS が  $10~\mu\mathrm{F}$  のコンデンサでカップルされているだけである。今回はノイズ特性を上げるために AVDD、AVSS と GND の間に  $100~\mu\mathrm{F}$  の OS コンデンサを並列に付け加えた。VA32TA チップの internal DACs の値は  $199~\mathrm{ビットのシフトレジスタ}$ でのみ制御するものとし、外部から internal DACs を調整するためのパッドにはワイヤボンドしていない。ひとつの Test structure には  $3~\mathrm{tm}$  を  $3~\mathrm{tm}$  があるが、もっとも良いエネルギー分解能を達成するためにストリップギャップが  $30~\mathrm{tm}$  と  $3~\mathrm{tm}$  と  $3~\mathrm{tm}$  のストリップを使用した。VA32TA、RC チップ、Test structure は直径  $3~\mathrm{tm}$  のアルミ線でワイヤボンドして接続をとった。読み出しシステム全体の写真を図  $3.1~\mathrm{tm}$  し、AC 結合モジュールと DC 結合モジュールの拡大写真を図  $3.1~\mathrm{tm}$  に示す。

### 5.2 データ解析の方法

Test structure と同じ p<sup>+</sup> 側の構造を持つ DSSD(P400×64) の全空乏層化電圧と同じ 70 V を Test structure と RCchip の Nsub にかけ、両者を完全に空乏化させる。読み出しを行

図 5.1: Test structure の複数チャンネル同時計測のためのセットアップ

図 5.2: AC 結合モジュール (左図) と DC 結合モジュール (右図)

わないストリップとバイアスリングは GND へ落とした。電源は Keithley Instruments 社製の Model 6517 を用いた。始めに AC 結合モジュールを温度 20 度の恒温槽に入れ、slow shaper の peaking time を  $2~\mu sec$  にして  $^{241}Am$  を照射した。 $1~\Phi$ のストリップで得られたそのままのスペクトルを図 5.3 に示す。この状態ではペデスタルがのっていて、ゼロ点があっていない。さらに、各イベント毎にコモンモードノイズがのっている。ペデスタルとは各チャンネル毎に存在するゼロ点からのずれ (オフセット) のことであり、コモンモードノイズは各イベントに対して全てのチャンネルが一斉に揺らぐノイズのことである。そこで、データ解析の方法として以下の手順をとった。

- 1. 他のチャンネルでトリガーをとったときのイベントを利用して各チャンネルのペデスタルレベルを求め、全てのデータからペデスタルを引くことで各チャンネルのゼロ点補正を行う。

- 2. 各イベントに対して波高値が最も高い2つと最も低い2つのデータを取り除き、残り のデータの平均値をコモンモードノイズとして全てのチャンネルのデータから引く。

- 3. 各チャンネルから得られた  $^{241}$ Am の 59.54 keV のピーク位置 (ADCchannel) を求め、その値を 59.54 keV とすることで各チャンネルのゲイン補正を行う。

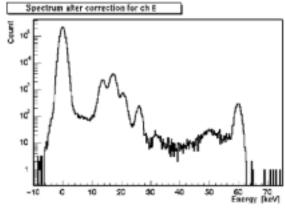

このような解析処理を施した後の同じストリップのエネルギースペクトルを図 5.4 に示す。 図 5.3 と比較してもわかるように、コモンモードノイズを引くことによって、エネルギー

ときの <sup>241</sup>Am のエネルギースペクトル

図 5.3: 得られたデータをそのまま用いた 図 5.4: 一連のデータ解析をした後のエネ ルギースペクトル

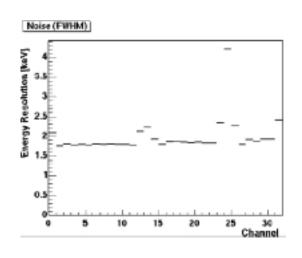

分解能の向上が確認できた。同じ解析を全てのストリップで行い、全ストリップのゼロ点 の揺らぎの大きさ、つまりノイズの大きさを求め、図 5.5 にまとめる。図 5.5 を見ると、ほ とんどのチャンネルでエネルギー分解能は約1.8 keV であるが、他のチャンネルと比べて エネルギー分解能が悪いチャンネルが存在する。0 チャンネルと 31 チャンネルは VA32TA チップの両端のチャンネルであり、12、13 チャンネルは Test structure のストリップギャッ プが  $160~\mu\mathrm{m}$  から  $130~\mu\mathrm{m}$  に変わるストリップであるため、少しノイズが大きい。24~チャ ンネルはうまくワイヤボンドすることができなかったため極端にノイズがのってしまい、 その両隣のチャンネルにも影響を及ぼしていると思われる。これらの悪いチャンネルを除 き、エネルギー分解能の良いチャンネルだけを用いて全てのデータを足し合わせた複数 チャンネル加算スペクトルを図5.6に示す。加算スペクトルのエネルギー分解能はノイズ の大きさで 1.7 keV、 59.5 keV のピークに対しては 1.9 keV であった。

得られたエネルギー分解能が理論的に予想される値と等しいかどうかを考える。VA32TA のアンプノイズは式 4.1 で表すことができ、 $\Delta E_{amp} = 1.4~{

m keV}$  になる。 ${

m RC}$  チップのバイ アス抵抗はおよそ  $1~G\Omega$  であり、ジョンソンノイズは  $\Delta E_{bias} = 0.3~{\rm keV}$ 、Test structure の リーク電流は  $70~\mathrm{V}$  で約  $430~\mathrm{pA}$  なので、ショットノイズは  $\Delta E_{lc} = 0.8~\mathrm{keV}$  となる。よっ て、ノイズのエネルギー分解能はこれらの2乗和で表すことができるので、 $\Delta E_{total} = 1.6$  $\mathrm{keV}$  となる。実際に得られたエネルギー分解能は  $1.7~\mathrm{keV}$  であり、ほぼ一致していること がわかった。

今後 AC 結合モジュールを用いるときはエネルギー分解能の悪いチャンネルではトリ ガーをたてずにデータを取得することにする。

#### VA32TA を用いた SSD 読み出しシステムの性能評価 5.3

SSD のノイズ成分をよく理解するために、AC 結合モジュールと DC 結合モジュールに 対して、温度 20 度と 0 度、shaping time が 2  $\mu$ sec と 4  $\mu$ sec の条件でエネルギー分解能

図 5.5: AC 結合モジュールのチャンネル とエネルギー分解能の関係

図 5.6: AC 結合モジュールを用いた  $^{241}$ Am の複数チャンネル加算スペクトル。測定条件は温度 20 度、shaping time = 2  $\mu$ sec

の測定を行った。使用した線源は  $^{241}$ Am と  $^{57}$ Co(122.1 keV、136.5 keV) である。DC 結合モジュールで測定する場合、VA32TA の両端のチャンネルと Test structure のストリップギャップが  $^{160}$   $\mu$ m から  $^{130}$   $\mu$ m に変わるストリップではトリガーをたてないようにした。それぞれの条件で得られたエネルギー分解能と理論的に予想されるエネルギー分解能の比較を表  $^{5.1}$  にまとめる。DC 結合モジュールを  $^{20}$  度で測定した結果がないのは、Test structure のリーク電流がそのまま VA32TA のフィードバック抵抗に流れ込んでしまい、正常に動作させることができなかったからである。

表 5.1: 実際に得られたエネルギー分解能と理論的に予想されるエネルギー分解能の比較

| 条件 | 温度   | Peaking            | ノイズ (FWHM)           |                    | エネルギー分詞                           | 解能 (FWHM)                         |